2016年11月,SIGLENT发布了新一代入门级示波器SDS1000X-E,它的最高带宽为200 MHz,采样率 1 GSa/s,标配存储深度14 M点;值得一提的是,SIGLENT将之前只在其中高端系列示波器上采用的SPO超级荧光数字示波器技术,集成到了这款入门级产品中,使其具备了灵敏度高、触发抖动小的数字触发系统,高达40万帧/秒的波形捕获率和256级辉度等级显示; 同时SDS1000X-E还支持丰富的数据采集和处理功能,包括智能触发、串行总线触发和解码、历史模式(History)和顺序模式 (Sequence)、丰富的测量和数学运算、高达1M点的FFT等等,重新定义了入门级示波器。

能够将一些中、高端数字示波器才具有的指标和功能体现到入门级示波器中,得益于SIGLENT在SDS1000X-E中使用了Xilinx的Zynq-7000 SoC作为核心处理芯片。

图 1 SDS1000X-E中集成了Zynq-7000

SDS1000X-E中采用的XC7Z020 SoC芯片,具有双核ARM Cortex-A9处理器(PS)+基于Artix-7架构的FPGA(PL),其中处理器部分支持的最高主频为866 MHz, FPGA部分则包含85k逻辑单元、4.9 Mb Block RAM和220个DSP Slice,并提供对常用外部存储器如DDR2/DDR3的支持,非常契合数字示波器中对数据进行采集、存储和数字信号

处理的需求。同时,Zynq-7000的PS(处理器系统)和PL(可编程逻辑)部分之间通过AXI高速总线互连,可以有效解决传统数字存储示波器中CPU与FPGA间数据传输的带宽瓶颈问题,有利于降低数字示波器的死区时间,提高波形捕获率。用单片SoC芯片替代传统的CPU+FPGA的分立方案,也可以减少硬件布板面积,有利于将高性能处理系统向紧凑型的入门级示波器中集成。

数据采集与存储

图 2 用Zynq-7000构架的SPO引擎

SDS1000X-E中采用的高速模-数转换(ADC)芯片,其数据接口为LVDS差分对形式,每对LVDS的速率为1 Gbps。采用的Zynq-7000芯片,其可编程IO的LVDS最高速率可达1.25 Gbps,可以保证稳定可靠地接收ADC采样到的数据。

同时,FPGA接收到的高速ADC数据需要实时地写入到存储器中,以8-bit,1 GSa/s的ADC为例,其输出数据的吞吐率为1 GByte/s。Zynq-7000支持常用的DDR2、DDR3等低成本存储器,最高DDR3接口速率可达1066 MT/s,因此,使用单片DDR3即可满足实时存储上述ADC输出数据的要求。而且,Zynq-7000支持PL共享PS的存储器,只要给PS部分预留足够的存储器带宽,剩余带宽用于存储ADC数据,无须在PL部分再外挂存储器,降低了成本。

更为重要的是,基于Zynq-7000中丰富的可编程逻辑资源(XC7Z020中为85k等效逻辑单元),SDS1000X-E集成高灵敏度、低抖动、零温漂的数字触发系统,使得其触发更为准确;各种智能触发功能如斜率、脉宽、视频、超时、欠幅、码型等,能帮助用户更精确地隔离出感兴趣的波形;总线协议触发甚至能直接用符合条件的总线事件(如I2C总线的起始位,或UART的特定数据)作为触发条件,极大地方便调试。

模拟触发

数字触发

图 3 模拟触发系统与数字触发系统的触发抖动对比

数据交互

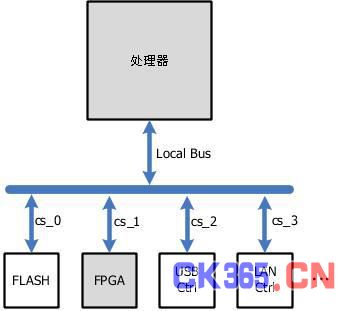

随着数字示波器设计复杂性的增加和处理器处理能力的提升,总线结构日益成为系统性能的瓶颈。传统的入门级数字示波器,采用低成本的嵌入式处理器作为控制和处理核心,采用低成本的FPGA实现数据采集和存储,二者之间通过并行的本地总线互连,处理器作为主设备,FPGA作为从设备;总线上同时还连接其他处理器外设,如FLASH、USB控制器等,如图 4所示。

图 4 传统架构的嵌入式处理器与FPGA互连

这种互连方式的最大问题是数据吞吐率低,一是因为本地总线一般是异步总线,理想的情况下一个读/写访问最少需要3个周期(1个setup周期,1个access周期和1个hold周期)。以16-bit位宽,外部总线频率100 MHz的本地总线为例,其理想的最高总线访问

吞吐率为66 MB/s;二是因为读、写操作共用一套地址、数据总线,属于半双工操作;三是多个从设备会竞争总线,从而降低每个从设备的有效数据吞吐率。以1 GSa/s采样率的数字示波器为例,其采样10 M点的时间仅为10 ms,但用于传输10 M点的时间(以理想的66 MB/s总线吞吐率为例)至少要150 ms,是数据采样时间的15倍。换一种说法,即使不考虑数据处理的时间,死区时间也达到了15/16 = 93.75%。

SDS1000X-E采用Zynq SoC架构,处理器(PS)和FPGA(PL)之间采用高速AXI总线互连,可以有效地解决二者间数据传输的带宽瓶颈问题,大大提高数据吞吐率,降低示波器的死区时间。Zynq-7000中采用的4个AXI-HP端口,每个端口支持最大64-bit位宽,最高250 MHz时钟频率;同时读、写通道分开,可执行全双工操作;PS和PL之间属于点到点传输,不存在与其它设备的总线竞争。使用单个HP端口传输数据,其吞吐率都可以轻易达到双向各1 GB/s的速度,4个端口总共可达到的读、写速率一共超过8 GB/s,远远大于本地总线的传输速率。

图 5 Zynq SoC中处理器与可编程逻辑的互连

数字信号处理

SDS1000X-E中配备了很多实用性高、性能强大的数字信号处理功能,如支持1 M点运算的FFT、增强分辨率(Eres)、14 M 全采样点的串行协议解码、14 M 全采样点的多种测量以及数学运算等,大大提高了入门级数字示波器的数字信号处理能力。

Zynq-7000丰富的硬件资源,为SDS1000X-E的数字信号处理功能提供了强大的支撑。SDS1000X-E中采用的XC7Z020 SoC芯片,PS部分具有双核ARM Cortex-A9处理器,最高主频为866 MHz, 并行协处理器NEON可以在软件层面执行数字信号处理;PL部分具有220个DSP Slice和4.9 Mb Block RAM;加上PS和PL之间数据接口极高的吞吐率,使得我们可以灵活地为不同的数字信号处理配置不同的硬件资源。

运算指令复杂、适合软件实现的功能,可以在PS侧实现,如信号上升沿的测量;需要使用大量乘累加运算,对硬件资源依赖度较高的功能,可以在PL侧实现,如示波器中常用的插值滤波。

有些复杂的功能,则可以利用PS和PL间的高数据带宽进行协同处理,例如FFT运算,在PL侧利用丰富的DSP Slice和Block RAM资源构建协处理器对基本FFT运算进行硬件加速,PS侧则实现复杂的窗函数计算、绘图、UI等操作。基于这种协同处理的架构,SDS1000X-E上的FFT支持高达1M 点的FFT,在获得极高的频谱分辨率的同时,还能大大加快频谱的刷新速度。图 6显示了在SDS1000X-E上分别进行16 k点和1 M点FFT的频谱分辨率对比。此例中我们给示波器输入了一个双音信号,其频率为100 MHz和100.05 MHz,从16 k点FFT获得的频谱图中我们无法分辨如此靠近的两个正弦信号,信号被作为一个频率显示出来;而1 M点FFT的频谱图有着明显更细致的频谱以及信号处理增益,从水平100倍展开的图中可以看出,两个相距50 kHz的正弦型号能够被很好地区分开。

图 6 1M点FFT获得极高的频谱分辨率

类似的,在SDS1000X-E还有诸多这种PS和PL间相互协同处理而获得的高性能数字信号处理。例如,SDS1000X-E可以对14 M 全采样点进行多种测量和串行协议解码,而这是在许多中、高端示波器中都做不到的。图 7中,上方两图为某主流中端示波器对10 ns上升沿的测量结果,下方两图为SDS1000X-E对相同信号的测量结果。可以看到,在小时基下,二者的测量结果都较为精确,与实际上升时间相差不大,但在大时基下,右上图显示该示波器在100 us/div下只能显示"< 48ns"的测量结果,注意此时它的原始采样率仍然有

1 GSa/s,这说明此时它的测量对象并不是原始波形数据,而是经过压缩后映射到屏幕上的数据。右下图显示SDS1000X-E在1 ms/div的时基下的测量结果,注意此时的采样率同样为1 GSa/s,但显示的测量精度仍然达到了1 ns,能够较为真实地反映信号的参数。

SDS1000X-E基于全采样点的数字信号处理以及高达14 M点的存储深度,允许用户在大时基下观察信号整体的同时,仍然能获得细节上的处理结果;同时由于其基于Zynq架构的处理方式,使得信号处理的性能和速度达到最优,具备更好的实时性和灵活性。

图 7 压缩点测量与全采样点测量精度对比