早在2009年初,IDC发布的预测:到2009年,几乎所有服务器、PC和笔记本电脑产品将全面实现多核化。虽然事实的发展再次验证了预测的准确性,但是实际情况有了新的变化。随着这些硬件产品在多核技术上的逐渐就绪,整个IT业界面临的最大挑战:如何将原先仅用于高端应用开发的并行编程方式推广到所有软件开发的过程中,以打造出更多支持多线程并行化运行的应用软件——尤其是处于关键地位的中间件,全面释放多核处理器的性能潜力。

为什么会是这样的结果呢?

原因是这样的:当时的中间件产品,尽管大部分都是基于多线程或者多进程的,但是由于传统单线程编程的思维定势以及开发语言和工具的限制,使得软件应用限制了多核处理器性能的发挥。对此,前微软首席研究官Craig Mundie称:“软件行业所面临的核心挑战就是对多核处理器的编程”。

前微软首席研究官Craig Mundie

相比 C/C++ 程序员而言,利用 Java 编写多线程应用已经简单了很多。然而,多线程程序想要达到高性能仍然不是一件容易的事情。当CPU 进入多核时代之后,软件的性能调优,已经不再是一件简单的事情,没有并行化的程序在新的硬件上可能会运行得比从前更慢。

为此,支持多核技术的操作系统应运而生,专门为充分利用多个处理器而设计,并且无需修改就可运行。为了充分利用多核技术,应用开发人员需要在程序设计中融入更多思路,但设计流程与目前对称多处理 (SMP,Symmetrical Multi-Processing) 系统的设计流程相同,并且现有的单线程应用也将继续运行。得益于线程技术的应用在多核处理器上运行时将显示出卓越的性能可扩充性,此类软件包括多媒体应用(内容创建、编辑,以及本地和数据流回放)、工程和其他技术计算应用以及诸如应用服务器和数据库等中间层与后层服务器应用。

1.多核处理器的主要优点

多核处理器主要具有以下几个显着的优点:

(1)控制逻辑简单

相对超标量微处理器结构和超长指令字结构而言,单芯片多处理器结构的控制逻辑复杂性要明显低很多。相应的单芯片多处理器的硬件实现必然要简单得多。

(2)高主频

由于单芯片多处理器结构的控制逻辑相对简单,包含极少的全局信号,因此线延迟对其影响比较小,因此,在同等工艺条件下,单芯片多处理器的硬件实现要获得比超标量微处理器和超长指令字微处理器更高的工作频率。

(3)低通信延迟

由于多个处理器集成在一块芯片上,且采用共享Cache或者内存的方式,多线程的通信延迟会明显降低,这样也对存储系统提出了更高的要求。

(4)低功耗

通过动态调节电压/频率、负载优化分布等,可有效降低CMP功耗。

(5)设计和验证周期短

微处理器厂商一般采用现有的成熟单核处理器作为处理器核心,从而可缩短设计和验证周期,节省研发成本。

2.多核处理已成为主流

不管是通用的微处理器,还是专用微处理器,乃至异构微处理器,都已经进入多核时代,通过多核技术提高处理能力,同时降低电能消耗已成为微处理器的必然选择。

随着半导体细微化进程,提高芯片性能和减少电能消耗成为一对矛盾。之前的单核处理器主要通过提高指令的并行运算速度来提高器件性能,这些复杂的计算处理耗用大量晶体管资源,使得微处理器在电能的消耗上一直无法降低,而多核结构的设计思路是通过减少并行处理,适当地降低每个核的工作强度来降低整个处理器的耗电。

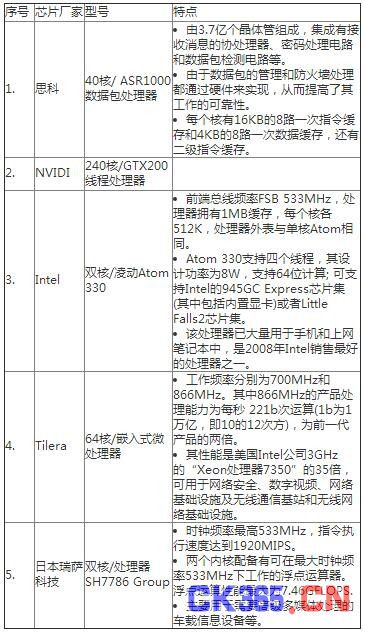

下面的两个表格,分别为各芯片厂商已经推出的具有代表性的多核处理器。

史上具有代表性的通用多核处理器芯片信息汇总表

以上专用多核处理器,通常具有4至9个核。而2016年最新发布的全新第七代智能Intel? 酷睿?处理器,将是4和8线程,默认主频高达4.0GHz。

专用多核处理器芯片信息汇总表

以上专用式多核处理器都有几十个核到上百个核。

在消费市场方面,市场上销售的个人电脑或服务器其处理器大多集成有2核、4核8核架构。近来,多核微处理器已开始进入通信和家用电器领域,可以说,多核微处理器将成为今后的潮流。