# 基于 DSP 和 CPLD 电能质量监测装置的设计

林广明1,黄义锋2,欧阳森1,蒋金良1

(1.华南理工大学电力学院, 广东 广州 510640; 2.广州普照科技有限公司, 广东 广州 510640)

摘要:设计了一种基于 DSP+CPLD 构架的电能质量监测装置,该装置利用 CPLD 产生 DSP 外围器件的控制时序,文中详细介绍了 CPLD 对 DSP 外围器件的逻辑接口设计,通过 MAX+PLUS II 对 CPLD 的控制时序进行仿真,仿真结果验证了本设计的可行性,试验测试结果表明该装置实现了多项电能质量指标的实时在线监测。

关键词: 电能质量; DSP; CPLD; 时序

## Design of a power quality monitoring device based on DSP and CPLD

LIN Guang-ming<sup>1</sup>, HUANG Yi-feng<sup>2</sup>, OUYANG Sen<sup>1</sup>, JIANG Jin-liang<sup>1</sup> (1.College of Electric Power, South China Univ of Tech, Guangzhou 510640, China;

2. Guangzhou Sunshine Electric Power Technology Co. Ltd, Guangzhou 510640, China)

Abstract: A new design of DSP+CPLD power quality monitoring device is proposed in this paper. And the CPLD( Complex Programmable Logic Device) is used to generate control timing between DSP and peripheral devices. In the paper, the use of CPLD in design of logic interface between DSP and peripheral devices is described in detail. The simulating result of CPLD control timing verifies the feasibility of the design and the testing results show that the device realizes on-line monitoring of power quality index.

Key words: power quality: DSP: CPLD: cycle timing

中图分类号: TM714: TM76 文献标识码: A

文章编号: 1674-3415(2009)18-0097-05

## 0 引言

目前,电能质量问题越来越受到人们的关注,主要的电能质量问题可分为稳态和暂态两大类,前者以波形畸变为特征,主要包括谐波、间谐波、波形下陷以及噪声等;后者通常以频谱和暂态持续时间为特征,可分为脉冲暂态和振荡暂态<sup>[1]</sup>。近年来,暂态电能质量的监测需求(例如毫秒级以下的脉冲暂态和振荡暂态)对监测装置的实时性和算法复理的在务种类繁多<sup>[2]</sup>,既有周期性任务(数据采样,各种计算、分析等),又有突发性任务(通信、人机交互等),同时还要保证系统的实时性,这就要求统处理器具有很高的处理速度、丰富的内部资源以及良好的逻辑控制能力。

目前,数字信号处理器(DSP)已广泛应用于智能化电力装置中,DSP应用需要解决的一个重要问题是 DSP 与外围器件(如键盘、液晶显示屏、扩展 RAM、ROM等)的时序配合和接口扩展<sup>[3]</sup>。由于DSP 性能有限,随着电能质量监测指标的细化,必

须引入其他措施来解决这个问题。文献[4]提出了基于双 CPU 的电能质量监测系统,由 DSP 完成实时分析计算任务,单片机负责完成液晶显示器、键盘等相对慢速的人机交互任务,但两个 CPU 之间数据的交换需要占用较多的系统资源。本文设计了基于 DSP+CPLD 构架的电能质量监测装置,利用可编程逻辑器件(CPLD)作为桥梁,实现了 DSP 与各种外围器件的时序配合,CPLD 的时序波形仿真与装置测试结果证明了装置的有效性。

## 1 系统硬件结构设计

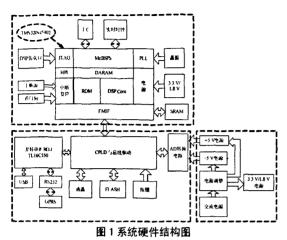

系统的硬件结构如图 1 所示。本装置的任务是完成对被监测信号的模数转换和各相电能质量指标的分析计算、存储和上传。硬件系统包括 A/D 转换单元、数字处理单元(DSP)、外扩程序空间 (SRAM)、外扩数据储存单元 (FLASH)、逻辑控制单元 (CPLD)、异步通信接口单元 (TL16C550)、人机接口 (按键、液晶显示)。

其中, DSP 采用 TMS320VC5402, 其运算速度 达 100 MIPS。CPLD 采用 EPM7128AE100-10, 其 内部集成了 2500 个可用逻辑门,具有 80 个用户可编程的 I/O 口,引脚到引脚的传输延迟仅为 7.5 ns。

Fig.1 Hardware structure of device

#### 1.1 CPLD 模块设计

CPLD 单元作为时序逻辑控制中心以协调整个装置的工作,CPLD 在整个电路中的逻辑控制包括:对 DSP 中断的管理,DSP 存储空间的选择和读写控制,A/D 采样和采样数据传输的控制,外扩程序空间 (SRAM)和数据储存单元(FLASH)的读写控制,LCD 显示的控制,对按键输入的响应控制,通信接口的控制。

以下将分别介绍 CPLD 对 DSP 外围扩展器件的逻辑接口设计(A/D 转换接口、通信接口和液晶显示接口),并详细分析了 CPLD 模块的时序仿真波形。

#### 1.1.1 A/D 转换接口设计

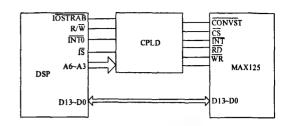

本装置使用两片 MAX125 分别对三相电压和三相电流进行同时采样。由于本装置采样率较高,如果采用 DSP 直接控制 ADC 的采集,将会占用较多的 DSP 资源;若采用 DMA 控制,则需要 DSP 支持总线挂起功能,DSP 需等待总线释放才能访问外部存储器和外部端口,极大地影响数据的及时处理。为此,本装置采用 CPLD 来实现 MAX125 的时序逻辑控制。

MAX125 与 DSP 接口电路如图 2 所示,图中,A/D 启动信号 CONVST、片选信号 CS、中断信号 INT和读/写信号(RD/WR)由 DSP 通过 CPLD 译码产生。由于 MAX125 的数据接口电平与 DSP 不匹配,故使用 SN74LVTH16245 作为电平转换器。MAX125和 SN74LVTH16245 的控制信号由 CPLD 发出。

图 2 DSP 与 MAX125 接口电路示意图 Fig.2 Sketch map of interface circuits between DSP and MAX125

#### 1.1.2 通信接口设计

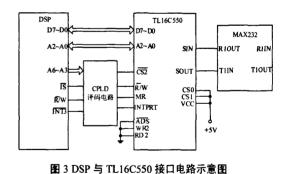

本装置采用 UART 芯片 TL16C550 实现 RS232 通信。TL16C550 的主要功能是为数据电路端接设备(DCE)设备和数据终端设备(DTE)之间提供可靠、灵活的接口服务。

DSP 与 TL16C550 接口电路如图 3 所示,TL16C550 的片选信号为 CS0、CS1、CS2 ,将 CS0和 CS1 直接置高电平,地址选通信号 ADS 直接接地(ADS=0时,片选信号生效,否则片选信号无效),则 CS2 为低电平时芯片被选中。TL16C550 提供低电平(RDI、WRI)和高电平(RD2、WR2)有效两种读写信号引脚。设计中将 RD2、WR2 低电平(无效状态),由 CPLD 译码来控制 RDI和 WRI 读写信号。TL16C550的中断请求信号 INTPRT(高电平复位信号)通过 CPLD 译码后与 DSP 外部中断信号 INT3 相连接。

Fig.3 The sketch map of interface circuits between DSP and TL16C550

## 1.1.3 液晶显示接口设计

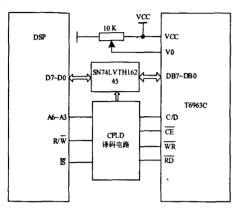

液晶显示模块的操作时间一般是毫秒级的,因此,液晶显示模块相对 DSP TMS320VC5402(运算速度为 10 ns)为慢速器件。本装置采用 SN74LVTH16245 来实现两者之间数据的缓冲,采用 CPLD 产生 DSP 对液晶显示模块的控制逻辑,液晶显示模块采用 DM12864F-6,其控制器为 T6963C.

图 4 为液晶模块与 DSP 的接口电路。C/D 为 T6963C 的通道选择信号,C/D=1 为指令通道,C/D=0 为数据通道;CE 为选通信号;RD,WR 为读、写选通信号;DB7~DB0 为 8 位数据总线。对液晶进行操作时,首先选通指令通道并写入相应指令代码初始化液晶模块,接着由 CPLD 译码选通数据通道,即可通过 DB7~DB0 对液晶进行相应的数据读写操作。

图 4 DSP 与 T6963C 接口电路图示意图 Fig.4 Sketch map of interface circuits between DSP and T6963C

## 2 CPLD 时序设计及其波形仿真

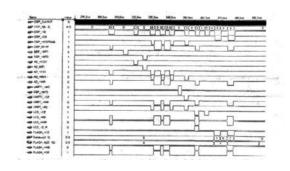

MAX+PLUS II 中的波形编辑器可以实现逻辑和时序仿真,设计中关键信号的时序仿真图如图 5 所示。图中,CPLD 的基准时钟为 DSP 的机器时钟DSP\_CLKOUT(100 MHz),各外围器件的片选信号由 DSP 的 A0~A3 地址线(DSP\_A[6..3])经 CPLD译码后产生,DSP\_~IS 为外围器件的使能输入端。

#### 2.1 A/D 转换过程

装置每工频周期采样 64 点,故 CPLD 每 0.3125 ms 触发 DSP 外部中断 DSP\_~INT1(低电平有效),在对应中断服务程序中将 AD\_~COV 置上升沿,启动 AD 转换。转换完成后,将 AD\_INT1 置低电平,经 CPLD 译码后触发 DSP 外部中断 DSP\_~INT0,在对应的中断服务程序中选通 AD (AD\_~CS1 置低电平),然后利用 DSP\_R/~W 和 DSP\_~IOSTRAB 信号经 CPLD 译码使 AD\_~RD1 连继三次有效,读取3个通道转换完成后的数字信号(另一 AD 芯片的控制与此类似)。当采样点数达到要求后,转入各种电力参数的计算程序中。

#### 2.2 FLASH 写操作

计算完成后, 使能 FLASH ~CE 信号 (FLASH

有效),同时利用 Databus[4..0](DSP 数据总线低 5 位)经 CPLD 译码控制 FLASH 高 5 位地址线 FLASH\_A[20..16],选择要写入数据的分页(FLASH 空间分为 32 页×64 Kbit),接着将写信号置低电平(有效),即可将计算的结果存入 FLASH 对应的空间。

#### 2.3 液晶显示写操作

当显示条件满足时,使能 LCD\_~CE 信号(LCD 有效)并置 LCD\_~D\_R 信号为低电平(选通数据通道),同时将写信号(LCD\_~WR)置低电平,即可将要显示的数据写入液晶 RAM 中,从而完成计算数据的实时显示。

## 2.4 异步串行通信过程

当有外部操作使 TL16C550 芯片中断信号 UART1\_~INT 有效(高电平),该信号经 CPLD 译码 后将触发 DSP 外部中断信号 DSP\_~INT3 使 DSP 进入相应中断服务程序(在 DSP 没有更高级的中断时)。在中断服务程序中, DSP 使能 UART1\_~CE(TL16C550 有效),同时产生 DSP\_R/~W 信号经 CPLD 译码后,分别控制 TL16C550 的读写信号 UART\_RD 和 UART\_WR 配合地址和数据总线,进行数据接收和发送。

图 5 中各信号的时序仿真波形符合各个芯片的接口要求,因此,本装置 CPLD 模块的时序逻辑设计是正确的。

## 2.5 性能改善

在没有采用CPLD之前,DSP5402只能进行每周期32点的采样和计算,远不能满足电能质量指标的计算和分析要求,而引入CPLD后,可进行每周期64点的采样和计算,且硬件资源利用率有了大幅提高。此外,CPLD的引入使得系统硬件设计更为紧凑,可靠性更高,开发和维护更为方便。

图 5 CPLD 关键信号时序仿真图

Fig.5 Cycle timing simulating results of key signal

## 3 系统性能测试

电能质量指标包括供电电压允许偏差、频率偏差、电压波动与闪变、三相不平衡度、公用电网谐波和暂时过电压和瞬态过电压<sup>[5]</sup>。限于篇幅,本文仅对电压偏差、功率、电压谐波(稳态电能质量)和电压骤降(动态电能质量)进行了试验,结果如下:

实验用经过中国计量科学研究院校准的标准

功率源 KS833 对本装置进行精确测量试验。

## 3.1稳态电能质量

表 1~3 为部分稳态电能质量试验结果,误差评价公式为:

绝对误差 = |测量值-标准值|

相对误差 = 测量值-标准值 ×100%

表1 三相电压测量数据

Tab.1 Voltage's measured data

| 标准源   | A相测     | B相测     | C相测     | A 相相    | B相相           | C 相相    |

|-------|---------|---------|---------|---------|---------------|---------|

| 输入值/V | 量值/V    | 量值/V    | 量值/V    | 对误差/(%) | 对误差/(%)       | 对误差/(%) |

| 220   | 219. 75 | 219. 45 | 219.79  | -0.11   | -0. 25        | -0.10   |

| 280   | 279. 83 | 279. 93 | 279. 89 | -0.06   | -0. 03        | -0.04   |

| 320   | 319. 82 | 319. 90 | 319.77  | -0.06   | -0.03         | -0.07   |

| 360   | 359. 73 | 359. 78 | 359. 89 | -0.08   | <b>-0.</b> 06 | -0.03   |

| 380   | 379. 73 | 379.66  | 379. 83 | -0.07   | -0.09         | -0.04   |

| 400   | 399. 77 | 399. 63 | 399. 53 | -0.06   | -0.09         | -0. 12  |

| 420   | 419. 51 | 419. 80 | 419. 75 | -0.12   | -0.05         | -0.06   |

| 460   | 459. 51 | 459. 77 | 459. 63 | -0. 11  | -0.05         | -0.08   |

注: 本表的测量数据是 10 次测量的平均值。

表 2 功率测量数据 (A 相)

Tab.2 Power's measured data(phase A)

| 电压标准值/V | 电流标准值/A | 单相输出功率/W | A 相有功测量值/W | A 相功率相对误差/(% |

|---------|---------|----------|------------|--------------|

| 60      | 0.3     | 14.40    | 14.45      | 0.35         |

| 100     | 0.8     | 64.00    | 64.02      | 0.03         |

| 220     | 1.5     | 264.00   | 264.28     | 0.11         |

| 300 /   | 2.0     | 480.00   | 480.33     | 0.07         |

| 350     | 2.5     | 700.00   | 700.42     | 0.06         |

| 380     | 3.0     | 912.00   | 912.21     | 0.02         |

注:本表的测量数据是 10 次测量的平均值。

表 3 电压谐波百分率测量值

Tab.3 Measured data of voltage harmonics rate

| 谐波次数       | 2     | 3     | 4     | 5     | 6     | 7     |

|------------|-------|-------|-------|-------|-------|-------|

| 标准值/(%)    | 5.00  | 5. 00 | 5.00  | 5. 00 | 5. 00 | 5. 00 |

| A 相测量值/(%) | 4. 99 | 5. 00 | 4. 98 | 4. 99 | 4. 99 | 4. 98 |

| B 相测量值/(%) | 5. 00 | 4. 99 | 4. 98 | 4. 98 | 4. 99 | 4. 98 |

| C 相测量值/(%) | 5. 00 | 4. 98 | 4. 99 | 4. 99 | 5. 00 | 4.98  |

注:本表的测量数据是10次测量的平均值,设定三相输入标准值均相同。

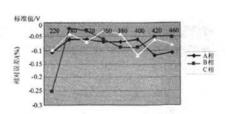

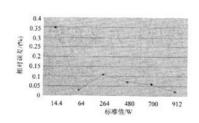

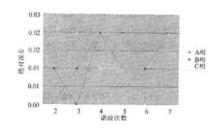

图 6~8 为三相电压和功率测量相对误差分布图和电压谐波绝对误差分布图,从图中可以看出,三相电压测量相对误差分布在-0.25%-0 之间,功率测

量相对误差小于 0.35%, 电压谐波百分率绝对误差 分小于 0.02%。

图 6 三相电压相对误差 Fig.6 Three-phase relative error

#### 图 7 功率测量相对误差(A 相)

Fig.7 Power's relative measurement error (phase A)

图 8 电压谐波百分率绝对误差

Fig.8 Absolute error of voltage harmonics rate

## 3.2 动态电能质量

电压骤降是暂态电能质量问题的一种,根据 IEEE Std 1159 的定义,电压骤降是指工频电压降低 0.1~0.9 p.u.之间,持续时间在 0.5 个周波到 1 min 的 暂态电能质量问题<sup>[6]</sup>。根据持续时间的不同,又可分为瞬时、暂时和短时电压骤降等三种类型,分别为 10~600 ms,600 ms~3 s 和 3 s~1 min。本文对电压骤降进行了测量实验,装置采样频率为 3.2 kHz,信号的最小分辩率为 0.312 5 ms,足以对这几种暂降信号进行检测。采用标准源 FLUKE61000 产生装置输入信号,装置监测结果如表 4 所示。

表 4 电压骤降试验结果

Tab.4 Voltage sags test results

| 电压骤降 | 输入信号次 | 准确监测 | 准确率  |

|------|-------|------|------|

| 类型   | 数     | 次数   |      |

| 瞬时   | 10    | 10   | 100% |

| 暂时   | 10    | 10   | 100% |

| 短时   | 10    | 10   | 100% |

从实验结果可以看出,监测装置具有很高的精 度,可以满足电能质量在线监测的要求。

#### 4 总结

本文设计了一种 DSP 和 CPLD 的在线式电能质量监测装置,采用 CPLD 来实现 DSP 与其它外围芯片接口电路的各种时序逻辑控制, CPLD 的引入使

得装置硬件结构紧凑,增强了系统抗干扰能力,保证了电能质量监测的实时性。在线仿真与实际硬件测试结果证明,该系统设计方案合理,性能稳定可靠。

#### 参考文献

- [1] 潘晓杰,刘涤尘,邹江峰. 基于 DSP 的电能质量在线监测装置[J]. 高电压技术,2005,31(12):73-75.

PAN Xiao-jie, LIU Di-chen, ZOU Jiang-feng. DSP-based Power Quality Online Monitoring System[J]. High Voltage Engineering, 2005,31(12):73-75.

- [2] 欧阳森,宋政湘,段成刚,等.新型电能质量监测系统的设计[J].电工电能新技术, 2003, 22(1): 43-47.

OUYANG Sen, SONG Zheng-xiang, DUAN Cheng-gang, et al. Design of a New Power Quality Monitor System[J].

Advanced Technology of Electrical Engineering and Energy, 2003, 22(1): 43-47.

- [3] PU Xiao-chuan, JIANG Lie-hui, ZHAO Qiu-xia, et al.

Time Characteristic Analysis and Circuit Design of

External Interface of Embedded System[A].

in:Proceedings of Computer-Aided Industrial Design and

Conceptual Design[C]. Hangzhou: 2006.1-5

- [4] 冯红岩,赵双喜,张建成,等.基于双 CPU 的电能质量监测系统设计与实现[J]. 继电器, 2006,34(7):61-64. FENG Hong-yan, ZHAO Shuang-xi, ZHANG Jian-cheng, et al. Design and Implementation of a Power Quality Monitoring System Based on Dual CPUS[J].Relay, 2006,34(7):61-64.

- [5] 肖湘宁.电能质量分析与控制[M].北京:中国电力出版 社.2004.

- [6] IEEE Std 1159-1995.IEEE Recommended Practice on Monitoring Electric Power Quality[M]. NewYork: IEEE Press,1995.

- [7] Ananth I, Morcos M M. A Power Quality Monitoring System: a Case Study in DSP-based Solutions for Electric Power Industry [J]. IEEE Trans on Power Engineering Review, 2005, 19(7):47-50.

- [8] Yang G H, Wen B Y. A Device for Power Quality Monitoring Based on ARM and DSP[A]. in: Proceedings of 1st IEEE Industrial Electronics and Applications[C]. Singapore: 2006. 1-5.

- [9] Antonio Delle Femine, Daniele Gallo, Carmine Landi, et al. Performance Analysis of Power Quality Monitoring Instruments[A]. in: Proceedings of Instrumentation and Measurement Technology Conference[C]. Canada: 2008. 2026-2031.

收稿日期: 2008-11-14 作者简介:

林广明 (1985-), 男, 硕士研究生, 研究方向为电能质量等; E-mail: gm.l@scut.edu.cn

黄义锋 (1984-), 男, 学士, 研究方向为电子测量仪器; 欧阳森 (1974-), 男, 讲师, 工学博士, 研究方向为电 能质量和智能电器等。

## 基于DSP和CPLD电能质量监测装置的设计

作者: 林广明, 黄义锋, 欧阳森, 蒋金良, LIN Guang-ming, HUANG Yi-feng, OUYANG Sen

, JIANG Jin-liang

作者单位: 林广明,欧阳森,蒋金良,LIN Guang-ming,OUYANG Sen,JIANG Jin-liang(华南理工大学电力

学院, 广东, 广州, 510640), 黄义锋, HUANG Yi-feng (广州普照科技有限公司, 广东, 广州

,510640)

刊名: 电力系统保护与控制 ISTIC EI PKU

英文刊名: POWER SYSTEM PROTECTION AND CONTROL

年,卷(期): 2009,37(18)

引用次数: 0次

#### 参考文献(9条)

1. 潘晓杰. 刘涤尘. 邹江峰 基于DSP的电能质量在线监测装置 2005(12)

- 2. 欧阳森. 宋政湘. 段成刚 新型电能质量监测系统的设计 2003(1)

- 3.PU Xiao-chuan. JIANG Lie-hui. ZHAO Qiu-xia Time Characteristic Analysis and Circuit Design of

External Interface of Embedded System 2006

- 4. 冯红岩. 赵双喜. 张建成 基于双CPU的电能质量监测系统设计与实现 2006 (7)

- 5. 肖湘宁 电能质量分析与控制 2004

- 6. IEEE Std 1159-1995. IEEE Recommended Practice on Monitoring Electric Power Quality 1995

- 7. Ananth I. Morcos M M A Power Quality Monitoring System: a Case Study in DSP-based Solutions for

Electric Power Industry 2005(7)

- 8. Yang G H. Wen B Y A Device for Power Quality Monitoring Based on ARM and DSP 2006

- 9. Antonio Delle Femine. Daniele Gallo. Carmine Landi Performance Analysis of Power Quality Monitoring

Instruments 2008

#### 相似文献(10条)

#### 1. 学位论文 唐亮 基于DSP的电能质量分析仪的硬件设计 2008

当今社会,存在大量非线性负荷(如电弧炉等),虽然他们对生产力的提高给与了很大的帮助,但它们也在电力系统中导致了严重的电能质量恶化。另外,得益于微电子技术的发展,各种自动装置广泛应用,而这些装置对于电能质量下降极为敏感,因此在生产实践中出现了许多严重的事故,造成了巨大的损失。当今,如何提高电能质量、确保用电设备安全稳定的运行,已成了国内外广泛关注的焦点之一。 本文设计了一种基于数字信号处理器的电能质量分析装置,利用DSP芯片强大的计算功能进行电能质量在线监测,实时显示测量数据,保存超标数据,为电网电能质量的测评和电能质量的改善提供了准确的依据。本装置作为电能质量在线监测系统的现场监测终端,主要安装在中、低压配电端、大型电力用户输入端等现场。 论文首先介绍了电能质量的概念,电能质量问题的提出,电能质量的测量方法,电能质量在线监测的要求和实现方法,以及DSP处理器在电能质量测量中的应用和发展、然后详细介绍了本监测系统的数据采样和模数转换设计、DSP电路设计和一些特殊功能模块,比如瞬变监测模块,锁相环模块。 本装置利用TI公司的TMS320C6713作为系统的中央处理器,实现了对多项电能质量的实时测量。为满足实时性的要求,在硬件上采用CPLD来完成系统的逻辑控制。实践表明,本电能质量综合测试装置具有很高的测量速度和测量精度,功能齐全,具有可扩展性,在性能和功能上优于同类产品,已经可以在配电网、工业园区等地方进行应用。

2. 期刊论文 <u>赵兵</u>. <u>刘春明</u>. <u>ZHAO Bing</u>. <u>LIU Chun-ming</u> <u>基于DSP与GPRS的电能质量监测系统</u> - <u>电网与清洁能源</u> 2009, 25 (2)

扶取广泛的电能质量实时监测数据具有重要的意义,但高成本和数据传输的不便限制了电能质量实时监测的范围.为此提出以GPRS作为数据传输通道组成电能质量监测系统,并使川单片DSP作为核心开发出低成本的电能质量实时监测终端,详细介绍了如何充分利用DSP的片内外围设备以简化系统硬件设计,同时介绍了软件的设计和在算法上进行的优化.

#### 3. 学位论文 谭子求 基于DSP的电能质量在线监测装置的研究 2004

如今,大量电力电子装置以及其它非线性负荷(如电弧炉等)得到了广泛应用,不幸的是,在提高生产力的同时它们也在电力系统中导致了严重的电能质量恶化.同时,微电子技术的发展使得各种自动装置广泛应用,极大地提高了社会生产力,而这些装置对于电能质量下降极为敏感,因此在生产实践中出现了许多严重的事故,造成了巨大的损失.当今,如何提高电能质量、确保用电设备安全稳定的运行,已成了国内外广泛关注的焦点之一.该文提出了一种基于DSP(数字信号处理器)的电能质量在线监测装置,利用DSP芯片强大的计算功能进行电能质量在线监测,实时显示测量数据,保存超标数据,为电网电能质量的测评和电能质量的改善进化了准确的依据.该装置作为电能质量在线监测系统的现场监测终端,主要安装在中、低压配电端、大型电力用户输入端等现场.论文的主体结构:首先介绍了电能质量的概念,电能质量问题的提出,电能质量的测量方法,电能质量在线监测的要求和实现方法,以及DSP处理器在电能质量则量中的应用和发展;然后详细介绍了该监测系统的数据采样和模数转换设计、DSP电路设计、通信接口设计和软件设计,以及系统的调试和测试。该装置利用订公司的TMS320VC5402作为系统的中央处理器,实现了对多项电能质量的实时测量,为满足实时性的要求,在软件上研究了高效的复序列FTT算法来分析谐波:在硬件上采用CPLD来完成系统的逻辑控制,利用UART(通用异步收发器)来进行申行通信,使DSP从繁忙的控制任务中解放出来。多种通信接口的设计,使得装置与外设通信十分方便。该装置还设计了友好的人机界面,操作方便简洁、实践表明,该电能质量综合测试装置具有很高的测量速度和测量精度,功能齐全,具有可扩展性,在性能和功能上优于同类产品,已经在配电网、工业园区等地方得到了很好的应用.

#### 4. 学位论文 王洪斌 基于DSP的电能质量监测仪设计 2001

该文在分析了现有技术和设备的基础上,采用DSP处理器TMS320F240,利用数字信号处理技术,设计实现了电能质量监测仪,并提供了与上位机通信的接口.该文详细介绍数字信号处理过程中的一些关键问题,并根据系统实际情况采用适应的方案.针对目前尚无统一的电能质量数据交换格式这一现状,该文根据IEEE的推荐标准,设计实现了电能质量数据交换格式PQDIF,并给出了应用实例.该文最后根据技术的发展,对系统的硬件和软件发展方案作了探讨,主要是一种基于分布式网络的应用方案

5. 期刊论文 周军. 李志霞. 陆勇. ZHOU Jun. LI Zhi-xia. LU Yong 基于DSP的电能质量在线监测系统的研制 -电测与 仪表2007, 44(7)

鉴于传统电能质量监测系统的缺点,本文提出了一种基于TMS320F2812的监测电能质量新方法.本系统主要利用快速傅立叶变换,对同步采样来的信号进行处理,从而对电能质量的五项指标进行分析、显示.实验结果表明,TMS320F2812对数据的处理速度满足实时性要求,本系统能够快速、准确地反映出电力系统中电能质量各项指标的变化情况.因此,本系统很好地适应了电力系统对电能质量监测的要求.

#### 6. 学位论文 邓少军 基于DSP的电能质量监测系统的设计与实现 2006

本文设计与实现了一种基于数字信号处理器 (DSP) 的电能质量监测系统,利用DSP芯片强大的计算功能进行电能质量在线监测,实时显示测量数据,保存超标数据,为电网电能质量的测评和电能质量的改善提供了准确的依据。本装置作为电能质量在线监测系统的现场监测终端,主要安装在中、低压配端、大型电力用户输入端等现场。 论文的主体结构:首先回顾了电力系统参数测量的发展历程,概述了电能质量问题的背景;其次、较为全面的论及了电能质量问题的现象。接着重点放在了电能质量的测量上,从有关标准入手,研究了各种分析方法以及测试仪器。最后实现了基于DSP的新型电能质量监测装置的软硬件设计,并对未来电能质量监测系统的研究做了简单的展望。 本装置采用TI公司的TMS320VC33作为系统的中央处理器,实现了对多项电能质量的实时测量。为实现预期功能,进行了以下关键技术的研究。在理论上,分析和实现了电能质量国家标准常规计算方法的数字化,采用连续信号计算公式的离散化近似,在保证一定精度的前提下,使DSP的高计算能力得已充分发挥;在软件上研究了高效的FFT算法来分析谐波,并灵活的应用中断技术优化DSP工作过程;在硬件上,采用锁相环技术来实现系统采样的逻辑控制,以达到同步的要求,接着对A/D转换输入信号的预处理电路进行了设计,在数据处理部分应用了性能优越的双端口存储器,实现系统的录波功能。最后设计和实现了系统各部分的电路连接,并结合实际需要设计了软件流程。 实践表明,本电能质量监测系统具有很高的测量速度和测量精度,功能齐全,具有可扩展性,在性能和功能上优于同类产

#### 7. 学位论文 刘毅 基于DSP的电能质量监测系统的研究 2007

随着大功率电力电子开关设备的普及应用,它所带来的各种电能质量问题已引起各国电力工作者的高度重视,提高电能质量的新技术已成为近年来 电力系统研究领域中新的研究热点。通过对电能质量进行实时监测、记录和分析,可以为改善电能质量、制定有关电能质量的治理措施以及确定治理装 置的技术参数提供必要的依据,这就使得研究电能质量监测技术具有十分重要的现实意义。本文以电能质量监测系统为研究对象,对电能质量参数的测 量方法和系统的软硬件设计做了详细的分析和研究,本文研究的主要内容有: (1) 在分析国内外对电能质量参数测量方法基础上, 研究了本课题的 电能质量参数的测量计算方法,详细讨论了一种基于布莱克曼窗函数的高精度FFT谐波分析方法,并经过仿真比对验证了这种方法能显著提高谐波测量的 (2)按照网络化、智能化、模块化的设计思路,设计了系统的技术指标,提出了系统的总体设计方案,构建了以DSP和CPLD为核心,包括信 精度。 号采集模块、DSP数据处理模块、CPLD逻辑控制模块、外扩存储模块、键盘及液晶显示模块和通信模块六大模块的系统总体架构。 总体设计思路,对电能质量监测系统的软硬件进行了分块设计:采用16位的A/D转换芯片,实现了对数据的高精度采样;采用主频1.50MHz的32位DSP TMS320F2812,实现了对高速采样数据的实时处理,提高了系统的数据处理能力;利用CPLD作为外围电路的逻辑控制模块,实现了对外围电路的灵活可靠 控制;键盘及液晶显示模块的设计,为系统提供了友好的人机界面环境;多种通信接口的设计,极大的提高了系统的通信水平,实现了网络化的总体设 计目标; 此外, 按照模块化的设计思想和本课题所采用的电能质量参数测量方法进行了程序的编写。 (4)根据系统总体设计要求,对系统硬件电路 及软件程序进行了分模块调试,给出了测试结果和试验波形,并对测试结果进行了分析。 通过对系统主要模块的测试表明,系统采样模块、数据 处理模块和通信模块均能正常工作,且测试的参数能达到系统的技术指标要求,实现了预期的设计目标。

8. 期刊论文 周丽. 钱荣银. 李文权. 蔡守平. ZHOU Li. QIAN Rong-yin. LI Wen-quan. CAI Shou-ping 基于DSP平台的电能质量分析仪的研制 -电气传动自动化2007, 29(4)

介绍了一种基于DSP平台的电能质量分析仪的研制. 通过DSP与ARM结合使用, 更有效地完成仪表的数据采集处理与显示. 详细介绍了电能质量分析仪的设计原理, 相关硬件和软件实现, 阐述了一种电能质量的分析方法.

#### 9. 学位论文 陈树 基于ARM和DSP技术的电能质量监测系统的研究与设计 2009

电能是一种最为广泛使用的能源,其应用程度是一个国家发展水平的主要标志之 随着科学技术和国民经济的发展,对电能质量的要求也越来越高。研制一种新型的电能质量实时监测系统,有效的进行电能质量监测,对保证电网和广大用户的电气设备和各种用电器具的安全经济运行、保障国民经济各行各业的正常生产和产品质量具有重要意义。 本文首先阐述了电能质量监测系统的国内外研究现状和电能质量的标准,并给出相应的测量方法:然后依据电能质量监测系统总体设计原则,详细分析了现有的各种设计方案,并比较各自的优缺点,最终提出了基于DSP和ARM的双CPU电能质量监测系统的设计方案。硬件设计方面,详细分析了更更元件的应用选型,重点研究了硬件平台的各部分组成和电路原理图。在前置采集模块中,采用ADS8364芯片设计了多通道信号采样保持和快速转换电路实现高精度的采样、利用锁相环跟踪电网频率实现硬件同步;同时充分发挥DSP的信号处理能力和ARM处理器的协调管理能力,设计了以DSP和ARM分核心的电路板。软件设计方面,ARM部分为构建了嵌入式Linux开发环境;DSP部分给出了程序设计流程图,应用程序中移植了嵌入式数据库家引ite,且设计了基于qt/Embedded的人机交互界面。

## 10. 期刊论文 祁红岩. 吕中志 基于DSP与ARM的电能质量监测仪的研究 -机电一体化2009, 15(10)

介绍了基于DSP和ARM的双CPU架构的电能质量监测装置,阐述了主要功能模块的硬件设计和软件设计.实验证明该设计方案不仅成功地满足了系统的高运算量,高空时件的要求。而且系统的改进和升级方便。易于功能扩展

本文链接: http://d.g.wanfangdata.com.cn/Periodical\_jdq200918021.aspx