# 应用手册 AN2233a

## 电容性开关扫描

作者:Dennis Seguine

相关项目:否

相关部件系列: CY8C21x34

PSoC Designer版本: 4.2 相关应用手册: AN2277

### 摘要

本应用手册简要介绍了采用CY8C21x34 PSo $C^{TM}$ 混合信号阵列的独特功能来实施电容性开关阵列的原理及设计方案。

### 前言

电容感应可以用作非接触式开关。如果采用绝缘层保护,这些开关可以抵抗恶劣的环境。本应用手册采用张驰振荡器进行电容测量,该振荡器的频率变化是电容值的函数。CY8C21x34器件系列的架构非常适用于扫描此类开关的大型阵列。

### 电容性开关

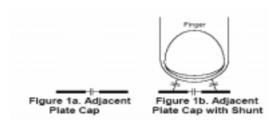

就其基本形式而言,电容性开关是一对相邻的平行板,如图1a所示。尽管存在较小的边缘至边缘电容(edge - to - edge capacitance),但开关布局的本意是为了最小化平行板之间的电容。如果将导体置于靠近两块平行板的位置,如图1b所示,那么就会在导体和一个电极之间产生电容,与此类似,导体和另一个电极之间也会存在电容。

用于任何导体,如导电的门锁开关、位置感应器,或者是触针式跟踪系统 (stylus tracking system) 中的导电笔。 电容开关阵列的最常见形式为:一组电容中每个电容

本例中的导体是手指,不过原则上这种方法适

电容开关阵列的最常见形式为:一组电容中每个电容的一侧均接地。这样,工作电容只有一侧可充电;开关是接地的可变电容。导体的存在加大了开关接地的电容。确定开关是否激活取决于电容测量是否发生了改变。

#### 电容测量方法

实际上存在数百种电容测量方法。较常用的方法包括:

**电流 - 电压相移测量**:采用固定值电阻驱动电容可以产生具有一定相位差的电压与电流波形。为了将相位测量保持在理想范围内,我们可相应调整驱动频率。

电阻 - 电容充电定时:采用固定电阻对电容充电,同时测量升压时间。为了达到合理的时间,较小的电容值可能会需要极大型的。

电容桥分压器 (Capacitive bridge divider): 此方法通过 固定的参考电容来驱动被测电容。参考电容与被测电容共同形成分压器。同步解调器即可恢复电压信号,在PsoC中可以轻松实现。

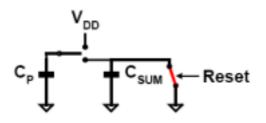

**电荷转移**:此方法在概念上类似于R - C充电电路。图2显著了简化的示意图。 $C_p$ 是需要检测的电容。 $C_{SUM}$ 为求和电容,电荷在连续周期中被转移至此电容。

图2:简化的电荷转移电路

$C_{SUM}$ 的电压在测量周期开始时复位。 $C_{SUM}$ 的电压随每个时钟周期呈指数(但幅度轻微)上升。我们可利用计数器测量此电压以达到特定阈值的时间。

#### 张驰振荡器

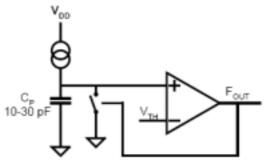

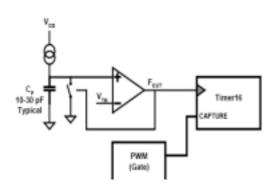

张驰振荡器由被测电容、恒流源、比较器以及复位开关组成,如图3所示。

图3:简化的张驰振荡器

对电容Cp进行线性充电,直至达到相应的阈值。此时,比较器输出变成高电平,从而启动开关闭合。然后电容放电,然后再次开始充电循环。

振荡器的输出频率取决于电容值和充电电流。

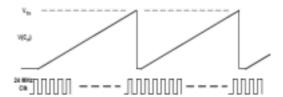

图4:张驰振荡器波形

比较器跳变时间和复位开关会增加固定的延迟。比较器输出与系统时钟同步,以确保比较器复位时间足以使 $C_p$ 的充电电压完全复位。这可为工作频率设定一个实际的上限。

注:此类电路常用作电容测量工具,通常采用可以实施比较器和复位开关的555定时器构建。 张驰振荡器电容测量的通用方式已经公布了数 10年。

### 计数.....

振荡器输出馈送至选通计数器(gated counter)用于测量。张驰振荡器的输出具有两种计数方法。在第一种方法中,振荡器输出驱动PWM的时钟输入。PWM的输出启动以系统时钟频率(一般为24MHz)计时的16位定时器。当PWM输出变成高电平时,通过释放采集控制开始计数。当PWM终止计数时,采集信号变成高电平,从而停止计数并且设置PWM的中断。在中断信号中读取定时器值。振荡器索引至下一个需要测量的开关,然后再次开始计数序列。

在第二种方法中,PWM按照系统时钟的派生频率、以固定周期计时。PWM的输出启动16位定时器。振荡器的输出为定时器计时。序列开始时Timer16复位;选通周期结束时读出计数值。此方法如图5所示。

上述两种计数方法在灵敏度与信躁比(SNR)方面具有相同的性能。第一种方法具有较快的数据采集速率,但是该速率取决于软件负载与开关电容值。第二种方法具有固定的开关数据采集速率。

图5:张驰振荡器测量

开关需要的计数长度和检测时间取决于灵敏度要求。如果 $C_p$ 变化较小,则频率变化较小。为了检测到较小的变化,可能需要进行长时间计数。这种电路的某些实施方法需要用到由固定电阻值编程的电流源。如果需要测量的电容范围发生变化,则必须调整外部组件(如:电阻)。

### PSoC实施 - CY8C21x34

CY8C21x34系列具有多种特性,可针对电容性开关扫描应用实现高效设计。这些特性包括:

- o 多路复用器阵列宽,从而可以由通用比较器与电流源测量所有通道。

- o DAC可调节电流源。

- o 比较器与复位开关自动连接。

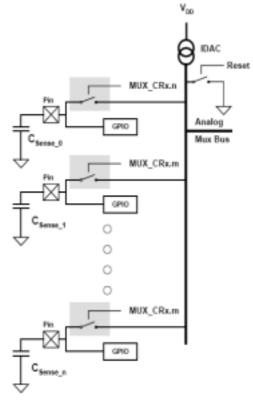

这种驱动与多路复用安排可以避免当前的GPIO把选择引脚连接至内部模拟Mux总线,如图6所示。恒流源(由寄存器DAC\_D控制的IDAC)与复位开关连接至模拟Mux总线。这样可以把引脚数需求降低到需要寻址的开关的数量;无需外部电阻或电容。

感应电容的电压取决于充电电流:

$$v(t) = \frac{i_{Charge}t}{C_{D}}$$

(1)

$C_{_{_{

m P}}}$  是铜箔及其连接器件之间的寄生电容。

图6: CY8C21x34 Mux总线结构

阈值设为 $V_{_{BG}}$ 。 达到此电压的充电时间为:

$$t = \frac{C_p V_{BG}}{i_{Charge}}$$

(2)

在达到该阈值时,比较器输出变为高电平,从而复位单个系统时钟周期的充电波形。典型的系统时钟频率为24MHz,因此复位时间为41.7nsec。此时间并入充电时间以确定振荡器频率。典型工作频率为200kHz~1.0MHz。因此,振荡器复位时间对工作频率的影响较小,而且相对固定。

振荡器输出在定时器中以一定时间 $t_{Count}$ 进行计数,而  $t_{Count}$ 取决于外部选通信号。需要读取计数器,以便获 取选通时间内的计数值。如果有手指或其它导体接触 开关,则电容提高到 $C_p+C_F$ ,从而使频率降低;在选通 窗口期间计数的张驰振荡器周期数也随之降低。

未接触开关时存储的值与当前值的差值可以确定是否 有手指接触开关。

$C_{_{\mathrm{P}}}$  一般情况下远大于 $C_{_{\mathrm{F}}}$  , 这样我们可以在几乎不影响精确度的情况下大大简化等式:

$$\Delta n = \frac{t_{Count}i_{Charge}}{V_{SG}} \frac{C_F}{C_F^2}$$

(3)

上式说明两个通道之间的灵敏度变量是两个通道的静态电容差值的平方的函数。为了确保独立开关的静态(寄生)电容理想匹配,在设计时需要做大量工作。这样可以提高检测的可重复性,使所有开关以相同的差值运行。上述变量可通过软件补偿。

通过代数换算,开关灵敏度的实际值为:

$$\frac{\Delta n}{n} = \frac{C_F}{C_P}$$

(4)

为了便于计算以及明确指示开关的启动, Δn必须具有足够大的值。这可以决定多方面的设计决策。

- 1.  $C_F$  应当尽可能远远小于 $C_P$  。 由于 $C_F$  取决于手指面积以及手指距离开关铜箔的距离(通过表层的绝缘体),因此应当尽可能降低 $C_P$  。  $C_P$  包含开关焊盘电容与寄生电容,寄生电容包括布线与芯片引脚电容。

- 2. 在开关阵列(即:多个开关)应用中,必须尽可能 降低灵敏度变量。如果△n差值较大,某个开关就有 可能在1.0cm距离时启动,而另一个开关可能直到 直接接触才启动。这并不是理想的方式。我们可以 采用多种方法平衡灵敏度。其中包括:

- a. 通过PCB线迹长度校正来精确匹配板上电 容·

- b. 在每个开关的PCB线迹上添加平衡电容;

- c. 对每个开关应用一个校准系数,每次测试 开关时使用。

- 3. 调整PCB设计,以降低电容,包括尽可能采用较厚的电路板。此时0.062" PCB优于0.015" PCB。

- 计数窗口应当足够长,以便Δn成为有效数字。"有效数字"可以低至10,也可以大到几百。例如C<sub>p</sub>是C<sub>p</sub>的10%(典型的"弱"开关),其中的开关阈值设为20的计数值,则n为:

$$n = \Delta n \frac{C_p}{C_F} = 2000$$

(5)

如果添加一定裕度使计数值达到2500,同时以1.0MHz的额定振荡器频率工作,则开关的检测时间为4ms。

#### 开关阵列设计

在许多电容式开关设计中,感应电容的两极实际上是相邻的铜箔或导线,如图1所示。其中电容一极一般需要接地。要制造开关,可以利用开关覆盖非常薄的相互交叉的线迹或者与周围接地层良好间隔的单个大面积焊盘。后一种构造允许范围更大的感应。线性滑动开关与轨迹板(trackpad)应用的布局采用紧紧相邻的开关。此时,未启动的开关全部通过相应引脚专用的PSoCGPIO接地。

相邻板(见图1)之间的实际电容很小,但是有源电路板(及其连接PSoC的PCB线迹)的对地电容可能较高。两个并列电路板的电容由下式求出:

$$C = \varepsilon_0 \varepsilon_r \frac{A}{d} = \varepsilon_r 8.85 \frac{A}{d} \frac{pF}{m}$$

(6)

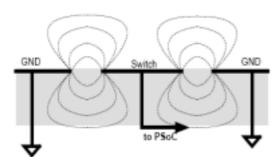

等式(6)中的计算单位为米。此为非常简单的模型。 实际上存在可以大大提高开关(和PCB线迹)对地电容的边缘效应。 图7说明从已有源开关到系统接地的磁场(注:磁力线旨在<u>说明</u>形状,而并非电场实际形状的准确描述)。借助合理的电路板厚度,电路板上面的磁场形状可以实现具有合理灵敏度的开关。

图7:开关的电场

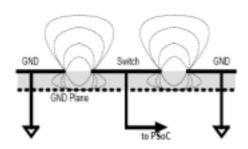

如果电路板结构包含一个位于开关下面的接地层,则 大部分电场将分流至该接地层,如图8所示。

图8:由接地层分流的电场

在开关下面采用接地层可以大大提高C<sub>p</sub>的值。通常的设计方法是把开关到PSoC的布线在远离开关的板侧即bottom层,同时top层铺地。每个开关的布线电容随布线长度变化而变化。把前侧(即top层)的接地层转变成密度为40%的栅格(如:交叉线层,在0.040"中心布置0.008"线迹或者在1.0毫米中心布置0.2毫米线迹)可以降低寄生电容。

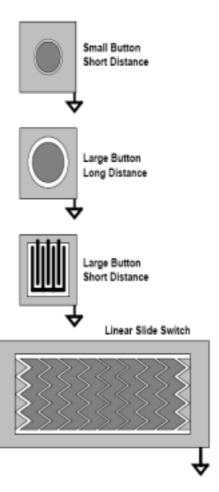

图9:典型开关模式

图9说明几种典型的开关模式。开关的工作范围取决于按钮和周围接地层之间的距离、覆层厚度与按钮间隙的比率、覆层厚度与按钮到接地层间隙的比率、以及材料的介电值。按钮尺寸的选择一般需要进行测试和优化。

虽然存在一定设计灵活性,不过开关材料通常取决于具体应用;设计人员可以通过选择适当材料提高SNR。大部分PCB材料( FR - 4 ) 挠性电路( Kapton或Mylar )、覆层材料( ABS ) 和玻璃的 $\epsilon_r$ 为4.0~6.0。低介电常数陶瓷材料的 $\epsilon_r$ 可以低于3.0。它们可适用于小型开关,其中封装的物理结构足以保护所采用的脆弱材料。开关背面的最佳材料、同时也是开关操作侧最不理想的材料显然是介电常数达到1.0的空气。

利用较高的SNR最易于实现开关感应,SNR定义为式 (3)中的 $\Delta$ n与系统噪声之比。系统噪声的来源包括计数过程中的量化误差、充电时间差值(作为电路输出 DAC中的噪声函数)、比较器中噪声造成的阈值变量、外部干扰信号、以及背景电容 $C_p$ 值的变量。上述电容会随PCB上开关的介质材料温度的变化而变化。利用软件可以自动补偿缓慢变化的环境条件。

如果开关和手指之间的覆层厚度低于PCB厚度的四分之一,并且PCB把非开关侧布置在接地层,则一般可以轻松实现理想的SNR。更开放的结构以及空气隔离可以提供更好的SNR,但是可能无法提供充分的屏蔽。

为了降低EMI以及对辐射灵敏度,设计过程中通常需要慎重安排PCB布局。尽管一般采用较大的面积,但是电容式开关阵列不会出现布局问题。不启动的开关接地(即:PSoC I/O的逻辑'0')。无论何时都仅仅启动一或两个开关。

PSoC GPIO输出不但较弱,而且速度也不快,因此不会产生辐射干扰。如果在个别开关及其到PSoC的布线下方采用接地层,则应当采用较为松散的栅格(0.040"中心上布置0.008"线迹)实现接地,以便降低寄生电容。这样可以保持低环路区域,从而降低辐射干扰并且提高辐射抗扰度。

#### 总结

PSoC CY8C21x34提供了独特而简洁的解决方案,能够利用单个芯片实现完整的电容式开关阵列测量。

### 作者简介

姓名: Dennis Seguine

职务: Cypress MicroSystems 公司高级应用经理

**背景:**加州大学伯克利分校 BSEE 与 MSEE。具有 30 多年的系统与模拟电路设计经验。在重要医疗设备方面拥有 5 项专利。从 2000 年开始担任 Cypress MicroSystems 公司应用工程经理。

#### 联系方式:

地址: 2700 162 Street SW, Building DLynnwood, WA 98037

电话: 800.669.0557 传真: 425.787.4641

电子邮件: seg@cypress.com

赛普拉斯半导体公司

地址:林恩伍德市 D 大厦西南街 162 号 2700

邮编:98087 电话:800.669.0557

传真:425.787.4641

http://www.cypress.com/

© 赛普拉斯导体公司 2005 年版权所有。保留全部权利。

PSoC™、Programmable System-on-Chip™和 PSoC Designer™均为赛普拉斯公司的 PSoC 相关商标。

本文提到的其他商标或注册商标均是其各自所有者的财产。

本文内容如有修改,恕不另行通知。美国制造。