在汽车电子中广为采用的微控制器(MCU)正快速面临时间和成本的压力。使用MCU的主要优势一直以来都是‘创造具有高性价比的高阶系统整合’。然而,在此一优势之下,有一些与元件本身相关的潜在成本是超乎于其单价水平的。例如,若选用的元件无法创造所需特性,则必须增加外部逻辑、软体或其它整合元件。

再者,目前汽车终端市场对于需求的变化屡见不鲜,以至MCU很快就变得不适用;许多具有专门特性以及固定专用介面数量的MCU,经过短暂的评估后即无法满足市场需求。因此,系统供应商不得不重新设计硬体及编写相关软体,在某些情况下,甚至必须更换处理器核心。

MCU的困境

MCU制造商正被迫面对会为整个市场带来巨大影响的挑战。MCU是针对应用而设计的元件;因此必须针对个别应用,设计具有不同性能组合的新元件。要以一个单一核心架构来满足这个广大市场,制造商必须提供多款MCU系列,提供不同的介面与功能。而市场上大部分的实例显示,目前的特性组合无法具体满足客户的需求,为了能够量产,必须在一个特定核心架构上改变新介面与功能。

过去的MCU是以旧有技术搭配相对低的制造成本来实现,在过去这是个成功的方法。但现在,为实现更高阶的系统整合,厂商不断采用先进制程技术,开发新的变种MCU所需费用变得相当可观。由于只有少数客户会下订单,因此,为满足单一客户需求而生产如此特殊的元件便不再具有商业意义。

因此,新的变种MCU被设计成具备越来越丰富的特性,以吸引整体市场,它正向标准产品发展,不再是针对特殊应用的元件。然而虽然这些标准产品的功能非常强大,但其成本也相对大幅增加,最后变得更难满足诸如汽车电子等对成本非常敏感的市场。

除了改变引起问题的根源——晶片上的固定功能,我们别无他法。很明显的,我们需要一种新的设计方法。

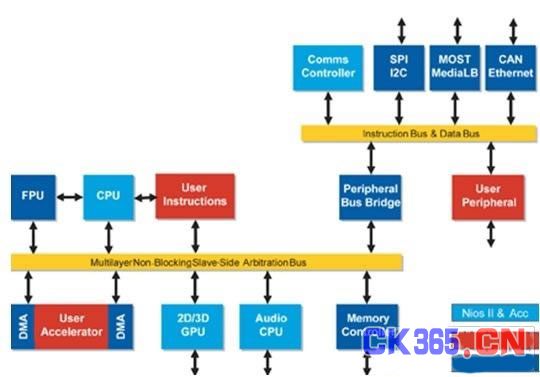

图1:此汽车资讯娱乐平台具有多个子系统、可扩展介面以及功能。

灵活的MCU概念

打破这个僵局的方法,是使用FPGA在晶片上实现灵活的功能。FPGA能显著缩短工程开发时间以及降低多次晶片返工成本,为MCU提供一个强而有力的可行替代方案。例如,采用基于FPGA的方法为汽车音响和导航设备开发一个灵活的绘图系统,可将开发时间缩短6个月。

与不具备所需特性的MCU不同的是,在设计过程中,可根据需要对FPGA进行编程和改编,以加快原型产生速度及产品上市时间。若需求改变,还可在现场对FPGA进行升级——即使元件已被安装在产品内。

相较于传统控制器,FPGA已成为汽车绘图控制器所采用的主要设计方法。虽然为了诸如绘图等独立功能所设计的低价FPGA能广泛地为汽车市场所接受,但为实现可编程能力,仍需在晶片上做出巨额投资,因此扩增的复杂功能也将使得可编程元件价格趋于昂贵。

但随着目前已能从FPGA无缝转换为结构化ASIC,一个灵活的微控制器已兼具了价格竞争力,它从一个预定义的大型元件库与可扩展建构模组中所选取的性能也可以具体满足客户需求。

它与传统MCU的主要区别在于,从原型FPGA到最终MCU的无缝转换过程。CPU和汇流排架构对灵活的MCU概念来说都是特殊的,且对于特定客户应用,它们可将所需特定功能及特性映射到设计中。

图2:FPGA到ASIC整合提升了控制器的性能和特性。

RISC CPU

在Altera设计概念中使用的CPU是软RISC处理器。然而,与一般情况不同,该处理器并不是建构在一个预先设定好、无法改变的晶片内。相反地,它采用的作法是依据系统架构师/设计工程师,借助可用工具定义的规格自动产生,并与整个电路所需的其余逻辑同时载入FPGA。因此对于特定应用需求,可使用相关开发工具对处理器核心进行参数化。更重要的是,它可根据所需功能以及实现这些所需功能所需的逻辑资源,无缝地实现设计。

在基于Altera的灵活MCU应用中,Nios II嵌入式处理器采用一款带32位元独立位址和资料汇流排的标准RISC架构。两个汇流排都透过独立快取记忆体执行,且可独立地连续馈送到汇流排系统。最后,系统架构师决定对程式码和资料采用个别记忆体或是两者共用记忆体。任何处理器包含的功能单元都呈现在Nios II嵌入式处理器中,根据不同设定决定它们的特性。例如可选择硬体乘法器、桶式移位器以及硬体除法器作为选项,同样地,对指令和资料缓冲记忆体进行精确的处理,其尺寸可不同或是彻底被排除在外。

汇流排架构

传统上在MCU内一直是采用单汇流排,一个仲裁器用于监控汇流排,以便使汇流排成为一种分散式资源。随著作为系统中心资源的汇流排迅速成为一项瓶颈,这种安排导致了严重的损害。因此,在较新的系统,特别是在许多汇流排平行工作的系统级晶片(SoC)上,已开始采用多层汇流排架构。目前FPGA的汇流排组织结构也以相似的原则进行,不同的是,在其他多层汇流排中所呈现的层数是固定的,但FPGA汇流排建构能让使用者依需求自由选择层数。

当考虑到电磁相容性(EMC)和功耗问题时,附加一个有别于整体系统执行功率的周边模组有时是合理的。举例而言,以较高速度执行一个记忆体介面,将可缩短存取时间,而系统内其余元件便得以较低的时脉速率运作。另一种方案是可在相对较低时脉便已足够的地方整合多个模组。

为满足EMC或功耗要求,采用诸如SOPC Builder等高阶系统设计工具可轻易地将这些部分与系统内以很高频率工作的部分分离。这些工具可自动产生同步这些不同时脉域所需的逻辑,而设计师只需指定在一个特定时脉域中执行哪些模组。

在FPGA内实现MCU

由于汽车MCU系统的复杂性比纯绘图控制器要高得多,所以FPGA大多用于原型逻辑产生。以FPGA产生原型能大幅降低开发风险,因为它能提供全面验证、韧体开发以及现场测试的功能。除此之外,藉由使用FPGA产生原型,设计师能以‘在系统内’的方式执行元件,并以真实情境的方式运作,以识别出一些模拟时没被侦测出的潜在设计缺失。

软体发展在整个开发周期中占了绝大部份。随着软体发展要花更长时间及更多资源,原型系统可缩短整个开发周期、发现设计缺失、解决相容性问题、缓解对新硬体功能的需求,以支援无法用软体有效处理或实现的功能。

用真实系统进行现场测试有助于察觉无法在实验室发现的系统或元件缺陷。在许多情况,销售人员为了说服客户提前下单,拥有一个展示系统是不可或缺的。

而一些在最初规格中没有的特性和功能也许也将成为必须。无论是因为之前没发现的缺陷还是必须需增加新功能,FPGA产生的原型都可以快速地被修改,无须一再花费巨额工程成本或忍受漫长制造周期。

灵活MCU概念中的最后步骤是ASIC开发。一旦建构并测试完原型系统,则可着手将设计转换为结构化ASIC。例如,若采用Altera元件,设计立即被转换为HardCopy结构化ASIC元件。与其它结构化ASIC不同,若采用该设计流程,则无须重新进行设计合成或花费额外的验证周期,因这些元件采用的是与其FPGA互补的构件。

采用该结构化ASIC流程提供的快速转换速度能让设计师快速签核FPGA逻辑,因而实现快速、低成本的转换。

本文小结

下一代汽车电子系统需要高度专用、成本最佳化的元件以满足市场需求。考虑到先进制程技术开发成本的急剧成长,对传统MCU针对特殊应用而设计的作法在商业考量上已不再适用。

针对广泛应用市场所设计的功能丰富型元件也因为过于昂贵而渐被市场淘汰。取而代之的则是灵活的MCU概念,只要将它安置在FPGA中来产生原型,就能提供为特定应用开发恰到好处MCU的程序。设计完成后,甚至在设计过程中可立即进行验证、软体发展和现场测试。

为进行量产,FPGA设计被直接映射为一个结构化ASIC而无须重新合成或额外验证。不只是软体发展,该方法实现了将硬体定义掌控在汽车电子系统设计师手中。创造了一种与当今任何固定功能MCU相比,均可花费更少时间以及更低成本的应用最佳化车用MCU。