WaveExpert CIS时基的最大记录长度是512 MS,采样率几乎是固定的10 MS/s。时基没有被触发,但要求与输入波形同步的外部时钟。必须把125 MHz到13.5 GHz的时钟频率连接到预定标器输入上,把62.5 MHz到125 MHz的时钟频率连接到触发输入上。CIS时基不支持62.5 MHz以下的时钟。

CIS时基使用锁相环(PLL),把大约2.56 GHz的内部时钟同步到外部时钟输入上。但是,同步是不确切的。它与外部时钟相差已知的量,基于一种算法,在PLL中设置相应的小数。额外的Divide By 256会从内部2.56 GHz时钟生成大约10 MHz选通。这个选通驱动一个采样器,采样器以计算的大约10 MS/s速率对输入波形采样。采样之间的时间大约为100 ns。采样之间将通过多个输入波形周期。它不要求触发,一旦时基同步到外部时钟上,可以以大约10 MS/s速率采集所需的多个样点。注意,采集4 MS的样点需要0.4秒。

CIS时基需要多个控制输入,包括Bit Rate, PLL Bandwidth, Pattern Length, Samples/UI和Ext. Divider。

Bit Rate

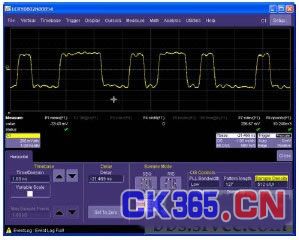

Bit Rate控制功能必须设置成码型的位速率或频率,即使码型是简单的正弦波或方波。下面是位速率设置成9 GHz、而不是10 GHz时的10 GHz正弦波实例。显示画面不能识别为一个码型。

注意水平描述符框中的失锁指示灯是红色,表明输入时钟速率与Bit Rate不同。作为示波器用户,您必须在Bit Rate控制框中键入输入信号的位速率或频率。

PLL Bandwidth

CIS时基有一个PLL,把选通输出同步到时钟输入上。PLL有两种带宽设置:Low和High,分别对应大约10 kHz和1 MHz,其使用PLL Bandwidth控制功能设置。CIS时基在Low设置上的时间抖动最低。如果想测量10 kHz以上的信号输入中的所有抖动,那么应使用Low设置。PLL将追踪DC到10 kHz的任意抖动,抖动将不会出现在被测信号上。如果想测量1 MHz以上的输入信号中的所有抖动,追踪DC到1 MHz的抖动,那么应使用High设置。

Pattern Length

通过在Std. Pattern选择框中设置Custom,或从提供的多个标准中选择一个标准,可以选择信号的码型长度。

下图是PRBS7和127的码型长度。CIS拥有杰出的功能,可以在没有触发源的情况下显示伪随机码型信号源。下面是长127位或27-1位的2 Gbit/s伪随机码型一部分的屏幕截图。

可以在某些限制下采集最长231–1或2147483647位的任意码型长度。

Samples/UI

可以使用Sample Density控制功能,改变每个位周期或单位间隔(UI)的样点数量。这个信号与上面8 S/UI时的信号相同。

注意码型中的水平位置与第一个屏幕截图中不同。在样点密度变化时,会重新编程内部PLL,相对于外部2 GHz时钟改变内部2.56 GHz时钟的相位。结果是码型的开始相位未知。只要Sample Density和Bit Rate不变或外部信号不变,那么相位将保持相同。

Ext. Divider

某些码型发生器拥有的输出时钟是除以码型位速率的时钟。注意在上面的屏幕截图中,Ext. Divider控制功能后面跟着一个输入时钟速率指示器,显示到采样示波器的实际时钟输入。

CIS Jitter

CIS时基拥有<250 fs rms的时间抖动。这只能使用低抖动信号源测量,信号源要拥有足够大的幅度和足够高的频率,以保证垂直噪声不会导致抖动。我们使用幅度大约为6 dBm的10 GHz正弦波测量抖动。信号源是安立合成信号源生成的正弦波。这个信号源的估计抖动小于150 fs rms。

下面是CIS时基采集的10 GHz正弦波的屏幕截图。

下面是测量CIS时基抖动使用的技术。把示波器连接到低噪声正弦波信号源上。这是使用的设置。

图示内容:

Power splitter: 功率分配器

Low Noise 10 GHz sinewave: 低噪声10 GHz正弦波

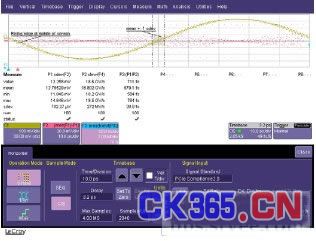

以下述方式设置示波器(参见下面的屏幕截图)。设置F1 = C1, F2 = eres(F1)-F1和F4 = eres(F1)。在这两个数学函数中,Eres都设置成3。使用F1 = C1,可以通过改变F1的来源,简便地改变测量通道。

数学函数F2平滑正弦波,去掉噪声,然后减去原来的正弦波,只剩下噪声。注意屏幕下面粉红色的F2曲线显示了零相交时的噪声,以及正弦波峰值时非常小的噪声。F2上屏幕中间的参数P1测量噪声的标准偏差。P1右面的门和左面的门移动到屏幕中间±0.2格内。

参数P2测量数学函数F4中平滑后的正弦波的转换速率。P2右面的门和左面的门移动到屏幕中央附近,测量被测的同一个边沿的转换速率。

P3使用参数演算,得到P1和P2之比,计算rms抖动。

在信号幅度很小时,必须考虑采样器的电压噪声。例如,在上面的设置中,采样器的电压噪声约为0.7 mV rms。从F2测得的标准偏差中减去这个积分值,得到实际标准偏差值:

实际标准偏差= sqrt(5.145742-0.72)=5.098 mV rms.

抖动从216.55 fs变成214.5 fs,略微调节了抖动。但是,如果正弦波的幅度下降,那么在零相交时测得的标准偏差将下降,现在采样器模块0.7 mV rms的电压噪声变得更加重要。如果降低正弦波的频率,也会发生这种情况,转换速率会下降,从而噪声在零相交时的标准偏差会再次下降。

如果使用更高带宽的采样器,电压噪声将更大,在使用上述技术测量抖动时,即使幅度相同,可能仍不得不考虑电压噪声。

下面是同一设置,但PLL Bandwidth设置成High。

增加的抖动是由于积分时在DC到1 MHz的时基抖动中增加的信号源抖动引起的。在正弦波零相交时,可以很容易看到时间抖动。再次注意,在正弦波的峰值上噪声非常小,说明了由于信号源和采样模块导致的垂直噪声很低。