本文首先将重点阐述汽车设计/可靠性方面的一些限制,然后会评测数字仪表群架构,以及存储子系统的取舍对于未来项目的性能、可靠性和成本有何影响。

数字式仪表群设计的挑战

数字式仪表群必须支持高性能实时处理需求(就像现有的消费级显示平台),同时显著提升设计的长期可靠性。汽车市场的OEM厂商(原始设备制造商)、一级供应商和客户绝不会将显示故障视为消费级电话或个人电脑经常发生的小问题。

新的数字式仪表群需要打造一种简单易用、排除干扰的信息环境,从而促进安全驾驶,这类产品必须确保出色的性能水平以及长期的可靠运行,同时承受苛刻而恶劣的工作环境(例如,-40~+105℃的极端温度范围)。

汽车行业在环境、安全和质量方面的这些严苛要求导致开发周期极为漫长,有时开发一项车辆显示技术需要耗时3年,甚至更久。

汽车设计的规划、设计和验证流程极为系统,以便找出并消除运行或可靠性方面的问题。此过程中,汽车设计师选择的电子元件供应商通常都采用TS16949等品质要求严格的设计方法开发产品,并且符合汽车电子委员会(AEC)苛刻的AEC-Q100标准。

一旦供应商推出量产系统,零配件供应商就必须持续监测其内部和外部的可靠性能,必要时采取纠正措施,确保缺陷零部件的百万分率(dppm)降到零。OEM厂商和一级供应商同样希望自己的供应基地能够提供长期的产品支持和可用性;一旦部署汽车嵌入式系统,再想停止就会产生高昂的成本,有时根本不可能为了支持寿命周期短暂的零部件而重新验证一款设计。某些情况下,重新验证的成本可能高达数十万美元。

数字式仪表群采用的图形内容与日俱增,导致信息显示系统更加精密复杂,这就不仅需要提高其性能水平,同时必须仍能可靠地完成基本目标,即通知驾驶人员基本的车辆和安全信息。

例如,数字式仪表群必须能在车辆发动之后以接近即时的方式提供车辆状态信息,通常不到一秒就能在TFT屏幕上显示重要的变速箱挡位信息(即P、R、D、1、2、3)。这就要求仪表群能够瞬间启动,而要实现这一点,设计师就需要仔细研究关键系统和零部件层面的性能表现。即使只是在车辆发动前提供胎压不足警告这样看似简单的信息,都能够预先主动减少潜在的安全问题。

仪表群从模拟系统向数字系统的过渡令人兴奋,但如上所述,这种过渡同样会提升复杂程度,设计师不得不发觉创新解决方案,满足苛刻的系统需求,例如实时显示性能、长期高度可靠及大幅削减成本等。

我们将研究如何以利用可靠而又极具成本效益的方式提供这些基本信息。

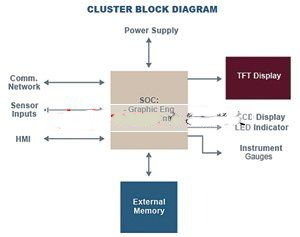

图1 高级数字式仪表群示意图

图1是一张高级数字式仪表群示意图。车辆的中央系统级芯片(SOC)通过其通信网络以及内部或外部存储器获取输入数据,并输出至TFT显示屏。数字式仪表群采用的系统架构同很多消费级高性能显示平台类似。

汽车和消费级显示平台都需要大容量存储器来支持各自庞大的数字内容;如今的汽车设计之中,3D图形内容、32位色彩、高分辨率和大显示屏的出现导致存储密度必须达到2Gb。

为创建内容丰富的显示系统,该内容通常包括大字符集、多种字体、图形影像以及多语言扩展支持。数字式仪表群帧缓冲会依照行业标准技术生成并显示。SOC显示控制器会在系统显示屏上渲染某一帧,同时SOC/图形引擎会访问内部或外部存储器,获取、处理、保存帧缓冲中的下一组数据,以供后续显示之用。当今的SOC需要以高带宽访问驻留在外部存储器中的可靠代码和数据,从而确保快速系统启动和高速实时处理。

数字式仪表群架构和存储器子系统的取舍

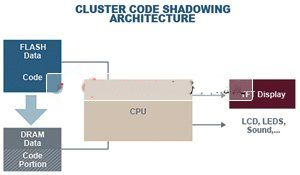

图2 标准代码映射存储器架构

存储器架构和设计实施会影响嵌入式系统的性能等级和可靠性。我们会评测若干种存储器架构,以便阐述采用当前技术可以实现的某些性能/成本取舍。首先,图2简单概括了标准代码映射存储器架构,高性能嵌入式显示系统通常都采用这一架构。

系统控制器或通用处理单元(GPU)的集成度很高,囊括了图形引擎、显示控制器,不仅提供限定容量的RAM和闪存存储器选择,同时依然提供外部存储器接口,从而满足数字仪表群对于高性能和高密度存储器的需求。

外部存储器分为两种标准产品:DRAM和闪存。嵌入式系统的启动主要分为3个步骤:首先是代码/数据从闪存映射到DRAM,然后处理器、DRAM和其他关键部件进行初始化,最后是执行应用程序。一旦开始执行代码,即会显示有用的信息。这种架构拥有若干关键特性。

SOC/DRAM的高速访问能力可以提升实时处理功能的性能表现。系统初始启动时间主要取决于映射和初始化的时间,而映射时间则取决于SOC/Flash访问带宽以及从闪存传输至DRAM的数据密度。

如前所述,高端数字式仪表群必须在车辆发动之后能以接近即时的形式提供当前的车辆状态。档位信息(即P、R、D、1、2、3)通常需在一秒之内显示在TFT屏幕上。这就要求闪存支持高速访问、超高存储密度和长期数据完整,以满足基本设计和质量需求,同时要求确定采购责任,确保产品长期供货稳定。

目前,闪存供应商可提供多种非易失存储器(NVM)技术,其中应用最广的两种技术就是NOR和NAND闪存。两者在各方面具有不同的性能特点,例如:访问能力、可靠程度、产品生命周期和成本。汽车SOC通常支持多种接口配置,以访问外部并行和串行NOR闪存,而NAND闪存接口正逐渐得到越来越广泛的支持。

请注意,SOC NAND接口的某个动态变量决定了所需的ECC支持级别,尤其是考虑到NAND正快速过渡到光刻技术。NOR方面,页模式和同步NOR闪存将继续满足汽车行业的严苛要求。例如,雪佛兰Volt的E-Flex仪表群等新型高端数字式仪表群设计采用飞思卡尔(Freescale)的MPC5121e型SOC和Spansion的S29GL512N闪存。Spansion GL页读取访问技术支持高速读取访问,其数据吞吐速率高达80MB/s,完全可以满足Volt E-Flex仪表群的需求,确保其在汽车启动之后的一秒钟之内显示变速箱挡位(即P、R、D、1、2、3)。

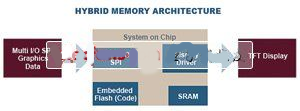

汽车芯片组和闪存供应商的不断创新催生出极具成本效益的全新混合数字式仪表群架构(如图3所示)。系统控制器(Freescale Spectrum)和闪存(Spansion Multi I/O SPI)可以优化TFT显示架构,提供更具成本效益的入门级仪表群解决方案。

系统控制器通过嵌入式闪存执行代码,同时利用高带宽多I/O SPI协议加载来自外部闪存的图形数据。图形数据在内部帧缓冲区进行处理并保存,然后直接显示到TFT屏幕上。这种大胆创新的混合架构无需外部DRAM存储器,不仅能够满足系统的性能和可靠性需求,同时可以优化成本。

图3 混合存储器架构

请注意,这种应用程序架构需要数以亿计的读取周期,因而会影响NAND这类技术的可用性。目前,NAND设备用于具有中、高读取周期的应用时,会出现更多的位干扰错误。

新型多I/O SPI通信协议可用于系统控制器和外部SPI闪存之间的数据传输。多I/O SPI基于流行的串行外围接口(SPI),其访问性能经配置可支持1?4个数据连接。这项功能可将SPI的访问能力从之前的不到10Mb/s提升至40Mb/s左右。

Freescale和Spansion等汽车芯片组和闪存供应商能够提供各种标准产品,保证设计师充分利用多I/O SPI经过改进的访问带宽,从而实现更好地控制成本,同时打造出性能出色的数字式仪表群。某些情况下,可使用两个四路I/O SPI,支持高达80 MB/s的连续吞吐速率。

Spansion的多I/O SPI FL闪存系列依然支持低引脚数串行接口,而且支持更高的读取带宽,堪比目前的多引脚数闪存设备。Spansion SPI FL系列同样可以满足中高存储密度和长期数据完整的要求,能够在高达105℃的工作环境中保持正常运行,同时符合AEC-Q100标准。