当今电力系统中的电能质量问题越来越突出,一方面,大量敏感性负荷对电能质量的要求越来越高,而另一方面,越来越多的非线性负荷不断接入电网,使电力系统总体的电能质量状况不断恶化。

谐波是电能质量中很重要的一个方面,谐波的存在对电力系统产生的危害有以下几个方面:

1)可能使电力系统继电保护装置和自动装置产生误动或拒动;

2)使各种电气设备产生附加损耗和发热,使电机产生机械振动及噪声;

3)谐波电流在电网中流动增加损耗,影响电网及各种电气设备的经济运行;

4)谐波电流通过电磁感应、电容耦合以及电气传导等作用,对周围的通信系统产生干扰;

5)谐波使电网中广泛使用的各种测量仪表产生误差;

6)增加了电网中发生谐波谐振的可能,从而造成很高的过电流或过电压而引发事故的危险性。

随着谐波污染的日益严重和对电能质量要求的提高,对谐波抑制的要求也越来越高,如何根据现场的谐波污染状况进行滤波器的投切也变得更加重要。针对这种情况,研制了一种谐波控制器,它可以对现场的谐波和无功等进行监测,根据现场谐波状况对滤波器进行自动投切,达到抑制谐波、改善电能质量的目的。下面介绍基于DSP芯片TMS32LF2407的谐波控制器的硬、软件设计。

1 谐波控制器的硬件设计

谐波控制器的基本原理是实时对电流、电压进行采样,将采到的数据经过D5P进行数据分析后,得到现场谐波的状况,从而决策是否对滤波器进行投切。

美国TI公司生产的TMS32LF2407型DSP芯片是一款高性能16位定点DSP,该系列DSP控制器将实时信号处理能力和控制器外设功能集于一身,特别适合于工业控制应用。其芯片供电电压为3.3V,降低了控制器的功耗。高达40M 1PS的执行速度(工作最高频率为40MEz),片内有32K字的Flash程序存贮器,544字的DARAM和2K字的SARAM,可以外扩存贮器总共有:194K字空间,片内集成了看门狗(WDT);提供多达16路模拟输入的10位A/D,最小转换时间为375ns;高达40个可单独编程或复用的通用输入/输出引脚。具有低成本、低功耗、高速运算能力和高性能处理能力的优点。因此,该DSP芯片可以满足作为此系统主控芯片的要求。

所研制的谐波控制器的硬件结构图如图1所示。

通过图1可知,此硬件电路主要包括采样电路、中央处理单元、复位电路、键盘和液晶显示功能、执行机构等几个部分。下面就硬件电路设汁中要特别注意的地方进行阐述:

1.1 采样电路

由于TMS32LF2407芯片的AD采样最大只能送入3.3V的电压信号,因此,在将电流、电压信号送到AD口之前要经过电流互感器和电压互感器进行调理,为了使引入的信号免受外界的干扰,互感器类型的选择和调理电路的抗千扰要特别地注意。此外,采样电路还应该要注意的一点是:由于TMS32LF2407的AD口很脆弱,也就是说AD口不能送入峰值超过3.3V的电压信号,否则AD口将被烧坏,因此,最好添加一个限幅电路。具体的调理电路如图2所示。

1.2 过零检测电路

为了使主芯片能够实现同步采样,进而提高数据处理的真实性,因此,在电路中应该加入过零检测电路。过零检测电路也就是方波发生电路,它对谐波分析同步采样起着很重要的作用。它将电压信号变为同频率的方波信号,DSP通过捕获方波的上升沿来跟踪电网频率,为保证同步采样提供了条件。具体的检测电路如图3所示。

1.3 执行单元

在执行单元中,继电器的供电电源是12V,而DSP的供电电源和IO口输出的高电平为3.3V,为防止高于3.3V的电压引入DSP,导致DSP的损坏,继电器控制信号的输出采用了光耦器件817进行隔离,继电器开关侧使用了阻容吸收电路来减小在开关开合时的冲击。具体电路如图4所示。

2 谐波控制器的软件设计

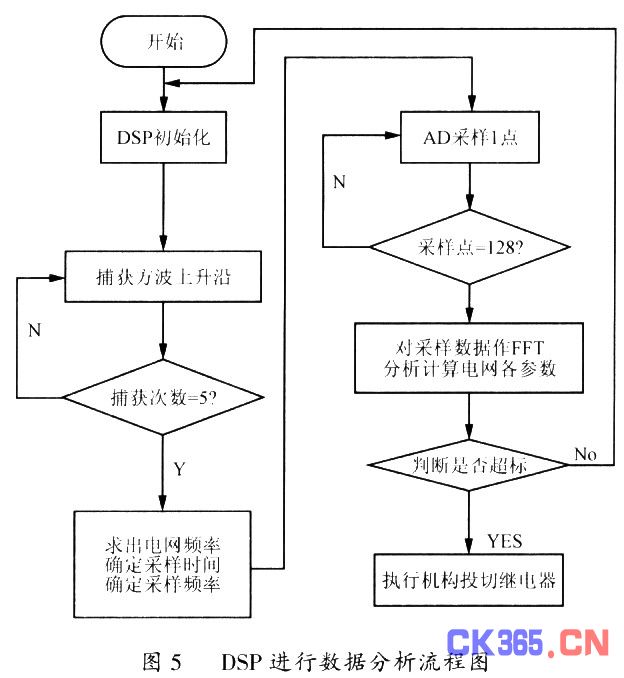

软件设计的核心就是对信号中的谐波分量进行分析,DSP在两个信号周期采样128个点,基于这些采样点进行快速付里叶变换(FFT)运算,从而分析得到信号中谐波的含量。谐波分量的分析精度取决于FFT的精度和同步采样。当采样频率是信号频率的整数倍时,即实现同步采样,采用矩形截断,并用FFT算法进行频谱分析,不会产生任何泄漏现象,可以精确重现信号频谱。如果能自动达到同步采样,对算法本身的要求就不需要太高,因为,同步采样后采用矩形窗进行FFT,矩形窗就意味着采样的数据可以直接作为FFT子函数的输入。过零检测电路就是为了实现同步采样,DSP捕获方波电路产生的方波上升沿,可以求出方波频率即信号频率。根据此频率可确定采样时间和两点间的采样间隔时间(两次AD转换之间的时间),通过这个方法就叮以实现同步采样,获得精确的频谱。每次FFT运算前都会重新根据实际电网情况改变采样策略,在几个周期内对电网频率的变化迅速作出反应,这样提高测量的可靠性和实吋性。

交流电压u(t)及电流信号i(t)每个周期进行N次采样,测得的离散值为u(n)、i(n),得到的离散化电压、电流有效值和有功功率计算公式为(N为采样点数)

![]()

根据P=UIcosθ可以求出功率因数,进而求得无功。根据FFT的结果可以得出各次谐波的含量,经计算可以得到总的谐波畸变率(THD),为DSP控制继电器投切滤波器提供了依据。

图5为DSP进行数据分析的流程图。

3 抗干扰设计

干扰主要有传导型和辐射型两大类,前者表现为干扰电流和电压,后者表现为干扰电场和磁场。影响智能脱扣器的干扰源有用电设备的浪涌电流;对讲机、手机等产生的射频辐射;智能脱扣器内部的开关电源和斩波释放电路等。这些干扰源的存在导致程序死掉,将干扰信号引入电流电压,从而使数据分析结果与实际差距较大,引起继电器误投切。为了减少千扰的影响,需要在硬件和软件上采取相应措施。

3.1 硬件抗干扰

采取的措施有:

1)合理布线,使数字电路地和模拟电路地共点接为悬浮工作方式,即系统各回路的基准电位互相连接在一起而不与大地相连,这样系统有较强的抗干扰能力;

2)模拟电路地和数字电路地分开接地,最后再汇合到一点;斩波泄放电路在启动工作后,出现很高的瞬态干扰,把逻辑地(主机)和模拟地(A/D)分开后,这种干扰就降到很低;

3)线路板和元器件表面喷绝缘层,这不仅是防潮和绝缘的需要,而且对防电磁千扰也有很重要的作用;在机壳内涂金属屏蔽层,形成等电位屏蔽,对电磁干扰也有很大的屏蔽作用;

4)在稳压电源、隔离变压器后侧安装滤波线路,这个滤波线路能使火线与零线中的千扰电流得到衰减;

5)弱电和强电之间常常需要隔离,常用的隔离方式有光电隔离、变压器隔离、继电器隔离等;本系统中采用光耦器件817对DSP输出的弱电控制信号与继电器强电进行隔离,由于光电隔离保证了DSP与继电器间无电的直接联系,从而保证了信号的正常传递,保证了DSP的安全。

3.2 软件抗干扰

软件上抗干扰的方法有以下几种:

1)为了防止装置收到干扰进入“死机”状态,在程序中加入一些监控措施利用看门狗(watchdog)对程序进行死锁检测,在必要的时候自动复位;在未使用的中断向量区、空白程序区设置软件陷阱,强迫程序跑飞以后能够回到正常轨道上来;在必要的地方写入冗余指令,以调整指令长度,防止程序混乱;

2)对采样信号进行数字滤波首先对每一个采样点进行判别,让其与相邻值、前次值以及增值最大值进行比较,根据对称检测法、限幅检测法来判断是否为干扰信号;对最近采样的点进行FFT计算得到的数据与前几次的数据求平均值,舍去“异类”。

此外,在数据处理的算法上进行改进,也能大大提高系统的抗干扰能力,但是,这往往是以牺牲代码长度为代价的,至于如何取舍视实际项目要求而定。

3.3 其他措施

在本系统中,DSP芯片除了进行数据采集和分析以外,还要实现对键盘和液晶显示的控制,这样DSP的工作量十分繁重,设计稍不全面就会出现中断冲突现象,为调试带来很大的困难。为此,可以采取在系统中添加一块单片机51芯片,用于管理键盘和液晶显示。现在单片机51芯片的价格十分便宜,系统中引入5l芯片不会导致成本过高。由于在正常运行时候,DSP和单片机通过双口RAM进行数据交流,其他内部的程序都不会相互干扰,因此,给调试带来了极大的方便,同时,最大可能地降低了程序跑飞的可能性。

4 结语

无源滤波器是抑制谐波的重要手段,它被广泛应用于电网的谐波抑制中,目前无源滤波器主要靠手工进行投切,这样既浪费人力,又达不到理想的效果,不能满足电能质量日益提高的要求。根据谁污染谁治理的原则,谐波污染也要由用户自己消除,因此,研制一种能对谐波进行监测控制的装置既方便了用户,又有广阔的市场前景。

1 2