关键词:光纤通道;IEEE1394;FPGA;协议转映射

航空电子系统经过几十年的发展,正在经历从模拟化向数字化系统的转变,逐步跨入第4代航空电子系统,其主要特点就是在第3代基础上,以高速大容量的信息交换为基础,从综合化向高度综合化发展,实现资源共享与数据融合,其任务划分、模块分配和作业调度,都依赖于数据网络系统的性能,这些性能包括网络拓扑结构、传输带宽、可靠性及数据延迟性能等。因此,未来先进航空电子系统中各站点之间的数据流将更为复杂,包括射频、视频等大流量数据,有的节点速率需求将超过1 Gb/s,而现有的低速数据总线很难满足如此高速的数据传输要求。

美国国家标准委员会于1988年开始制定的光纤通道(Fiber Channel,FC)是一种高速串行总线协议,不仅具有高带宽、高可靠性、低延时、传输距离远、拓扑灵活的优点,而且支持多种上层传输协议。光纤通道的这一优点使得在同一物理接口上运行多种上层通道标准和网络协议成为可能。目前已经实现的ML-STD-1553到光纤通道协议的映射,以及ML-STD-1553远程终端器件与光纤通道互联方案的系统综合,为未来航空电子系统中不同总线的互连提供了一条新的途径,使得系统在保留传统网络拓扑和协议的同时,获得光纤通道所提供的高带宽服务。

基于此设计思想,本文提出了一种IEEE1394到光纤通道传输协议的映射方案,在此工作基础上,利用现场可编程逻辑阵列(FPGA),对所提出的协议映射方案进行了硬件设计与实现,设计了一个基于FC的IEEE1394光信号传输系统。

1 IEEE1394到光纤通道的协议映射

首先简要介绍本文提出的一种IEEE1394到光纤通道传输协议的映射方案,更详细的说明可参考文献。所提协议映射方案的基本思想是:在IEEE1394到FC数据包的映射过程中,保留FC原来的帧格式形式,将FC帧头部分中源节点和目的节点的地址分别映射为IEEE1394源节点和目的节点的地址,并将IEEE1394数据包中除了数据域外的其他信息映射到FC的64 Byte可选帧头上,数据域的信息映射到FC的有效数据区。此外,由于FC一个数据帧的有效数据区长度只有2 048 Byte,而在通道传输速率大于200 Mb/s,IEEE1394的等时数据包或传输速率大于400 Mb /s时,异步数据包的最大有效长度将超出FC有效数据区的大小。因此,当IEEE1394数据包的长度超出了FC有效数据区长度时,应该将该数据包映射成一个连续的FC数据帧序列。下面以IEEE1394异步数据包到FC数据帧的映射为例,说明两种协议的映射过程。

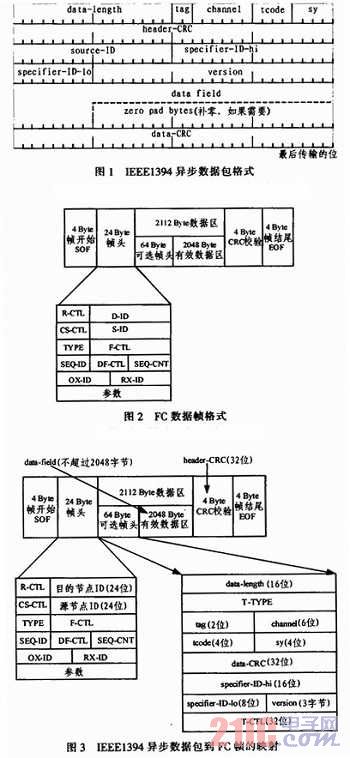

IEEE1394异步数据包及FC数据帧格式如图1,图2所示。图3为IEEE1394数据帧到光纤通道帧格式映射关系。

对映射过程的说明:

1)目的节点和源节点地址由IEEE1394的16位扩充到24位,使网络规模变得比单一的IEEE1394网络要大。

2)T-TYPE用来指明交换消息的传输特性,包括交换的传输方向和终端-终端(NT-NT)交换的性能定义。在NT-NT类型交换中,将为接收NT提供发送NT的地址,或者为发送NT提供接收NT的地址。

3)T—CTL用于实现FC网络和IEEE1394网络之间的消息传输,实现两者之间的桥路连接,完成FC网络终端或网络控制器与IEEE1394节点之间的消息传输。

4)将IEEE1394中的帧头CRC校验和数据CRC校验分开。在IEEE1394数据传输中,首先进行的是帧头CRC校验,如果发现错误,则立即抛弃该帧。所以这里设想将IEEE1394数据CRC放在光纤通道数据帧的可选帧头,将帧头CRC放在光纤通道数据帧CRC校验中,这样可以先检测帧头CRC,节省系统开销。

2 IEEE1394光信号传输系统设计与实现

2.1 系统的构架

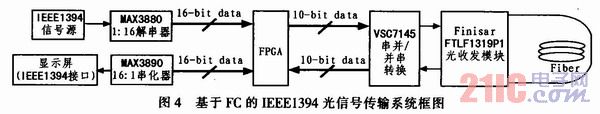

为在光纤通道传输IEEE1394信号,构建两种总线互连的硬件平台,所设计的传输系统不仅要实现两种数据帧格式的转换,还要实现FC-0、FC-1、FC-2协议层中的部分功能。本文所设计的基于FC的IEEE1394光信号传输系统结构如图4所示,包括IEEE1394信号源,基于FPGA的1394-FC协议转换器,必要的外围接口器件以及光纤收发模块,系统传输速率1.062 5 Gb/s。其中,光纤通道FC-0层的功能由光电转换模块和串并与并串转换芯片实现,而IEEE1394到FC数据帧映射及FC-1、FC-2层功能主要基于FPGA进行硬件编程来实现。

2.2 基于FPGA的功能模块设计与实现

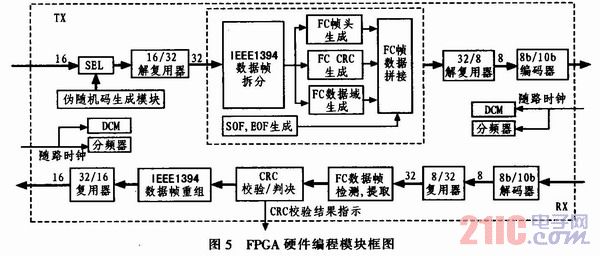

在所设计的系统中,FPGA主要实现IEEE1394到FC的数据帧映射以及FC-1、FC-2层功能。基于FPGA的功能模块结构如图5所示。

1)FC-1层功能单元包括8 b/10 b编码/解码模块和D/K类型指示模块。

2)FC-2层功能单元包括数据接收模块,发送模块及系统配置模块。

3)IEEE1394到FC的数据帧映射模块(协议转换)是FPGA设计的核心部分。该部分能够完成对信号源发出的IEEE1394数据帧到FC协议的数据帧的映射工作,即将IEEE1394数据帧转换为FC帧格式。同时能从接收到的FC数据帧还原出IEEE1394数据帧。

4)FPGA片内的发送(TX)部分和接收(RX)部分均加入了数字时钟管理(DCM)和分频器模块,DCM可以使时钟信号通过时钟树达到各个片内寄存器,以减小片内时钟信号的抖动和延时,提高系统运行速率。

此外,为了方便在没有外接IEEE1394信号源的情况下对FPGA内部的功能模块进行调试,在FPGA的TX前通过采用线性反馈移位寄存器IP核构建了一个伪随机序列发生器,可以用来模拟IEEE1394数据源,并通过1个二选一选择器实现外部输入信号与内部伪随机序列的选择功能。

FPGA内部的工作过程说明如下:IEEE1394数据从16:32解复用器输出之后,进入IEEE1394数据拆分模块,产生对应于FC数据帧的SOF、DATA、CRC、EOF的数据段,生成符合FC帧格式的数据。在这之后,32:8复用模块将32 bit并行输入的数据复用成8 bit并行输出的数据。随后进入8 b/10 b编码模块,完成8 b/10 b的编码工作并以10 bit位宽,106.25 MHz的速率送入VSC7145串并/并串芯片,最后以1.062 5 Gbs的速率输出到SFP光收发模块,由光收发模块将电信号调制成光信号输出。

在RX接收部分,由光收发模块还原成的电信号通过VSC7145串并/并串芯片后以10 bit的并行数据形式输入到FPGA中,由8 b/10 b解码器解码,输出8 bit并行数据(在解码过程中,解码器可以通过判断码流的极性来判别是否在传输过程中出现误码)。8 b/10 b解码输出后的数据通过1个8:32解复用模块解复用成32 bit的并行数据,并行支路速率为26.562 5 MHz,随后32位并行数据通过FC帧检测提取模块,生成标识信号随路输出。在CRC校验/判决模块中,数据通过CRC位运算反映是否出现误码,并给出指示。在这之后,FC数据帧重组为IEEE1394数据帧,最后经由32:16复用模块将32 bit并行IEEE1394帧数据重新复用成16 bit并行数据,与53.12 MHz的随路信号一同送出FPGA芯片。

3 FPGA功能验证

本设计已在Xilinx Spartan3系列的Xc3s200中实现,并在Xilinx ISE 7.1仿真环境下进行了功能和时序仿真验证。采用伪随机序列发生器生成的伪随机代码模拟IEEE1394数据源,设定每1 000 Byte为一个数据包包长。

3.1 功能仿真结果

1)在发送端,IEEE1394数据包被拆封,重组成FC数据帧,并由8 b/10 b编码器编码后输出,如图6中仿真波形tx_dtout,和TX_encode_ dtout所示。

2)在接收端,FC帧结构被正确检测并提取,在CRC校验正确后重组成IEEE1394数据帧格式输出,如图7中仿真波形tx_dtout,crc32及rx_dtout所示。

经仿真测试,FPGA实现IEEE1394到FC数据帧格式的映射功能,各模块均正常工作,数据通信良好,无丢包现象。

3.2 时序仿真结果

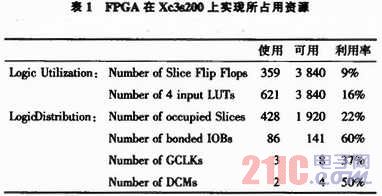

该设计在Xc3s200上实现后,FPGA所使用的资源如表1所示,整个系统资源占用率较低,最高运行速率能达到135.245 MHz,满足106.25 MHz的片上最高运行速率要求,设计达到了预期结果。

4 结束语

光纤通道具有支持多种上层传输协议的优点,本文在已有工作的基础上,利用FPAG,对所提出的IEEE1394到光纤通道的协议映射方案进行了硬件设计,通过FPGA功能仿真及时序仿真验证了所提方案的可行性。利用此FPGA协议转换模块,本文还设计了基于FC的IEEE1394光信号传输系统,给出了具体的硬件设计方案。目前,此系统的主要调试工作已完成,后续的工作将通过系统传输实验,对系统性能进行分析研究。