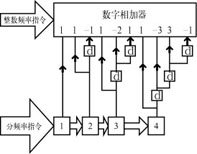

很多方面都有广泛的应用。在一个小数分频项目中,需要构建一个四级的pascal三角形来进行相位补偿,如图1所示,第二个累加器的溢出必须通过第一个微分控制分频比,第三个累加器的溢出必须通过第二个微分控制分频比,依此类推。第二个累加器使分频比变为N+1、N-1,第三个累加器将分频比变为N+1、N-2、N+1,第四个累加器的分频比序列为N+1、N-3、N+3、N-1,正如图2所示该序列构成一个pascal三角形,每行的总和为零。依照这个规律可以设计实现pascal 三角形运算的通用电路。

很多方面都有广泛的应用。在一个小数分频项目中,需要构建一个四级的pascal三角形来进行相位补偿,如图1所示,第二个累加器的溢出必须通过第一个微分控制分频比,第三个累加器的溢出必须通过第二个微分控制分频比,依此类推。第二个累加器使分频比变为N+1、N-1,第三个累加器将分频比变为N+1、N-2、N+1,第四个累加器的分频比序列为N+1、N-3、N+3、N-1,正如图2所示该序列构成一个pascal三角形,每行的总和为零。依照这个规律可以设计实现pascal 三角形运算的通用电路。Pascal三角形的数学描述

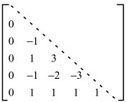

pascal三角形通常用三角形的方式来表示,如图2所示,也可以用一个二维的下三角矩阵来描述,如图3所示。

矩阵a[n,n]可以用下面的公式来描述。

a[i, j]=a[i, j-1]+(-1)a[i+1, j] (式1)

(a[n, 1]=0,a[n, 2]=a[n, 3]=...=a[n, n]=1)

i≥1,j≥2。

矩阵中第一列的0是为了方便电路实现而人为加上去的。将此二维矩阵表达式(即式1)变成含有时间的一维方程。

a[i]j=a[i]j-1+(-1)a[i+1]j (式2)

i,j均大于1,a[n]2 =a[n]3=...a[n]n=1。下标表示时间,a[n,1]=0表示刚开始整个电路的清零信号,其余第一

i,j均大于1,a[n]2 =a[n]3=...a[n]n=1。下标表示时间,a[n,1]=0表示刚开始整个电路的清零信号,其余第一 列的0表示对应pascal三角形的和为0,最后一行的1表示pascal三角形每一行对应的输入端有输入值1时,产生的立即数为1。

列的0表示对应pascal三角形的和为0,最后一行的1表示pascal三角形每一行对应的输入端有输入值1时,产生的立即数为1。 此外,式2具有叠加性,可以把pascal三角形中的一行加上其余任意一行或者几行,实现任意时钟周期的延时。

Pascal三角形的基本电路

根据上面一维含时公式,先要构建补码电路,然后是一个加法电路,最后是一个延时电路。

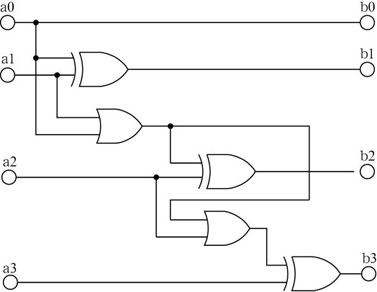

假设一个数组a[n:0]表示数的各位,a[0]为最低位,对各位取反,然后最低位加1,得到一个新的数组b[n:0],这个数组最低位为b[0],对应的逻辑关系是:

其余位按照这个规律依此类推,逻辑图如图4所示。

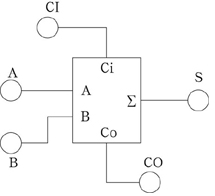

采用通用的全加器,逻辑表达式为:

示意图参见图5。其中CI为上一级的进位,A、B为本级输入信号,S为全加和,CO是本级进位。

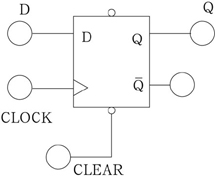

延时器采用带清零的D触发器来实现,见图6。CLOCK为时钟信号,CLEAR为清零信号,D是数据输入信号,Q是原量输出

。

电路设计

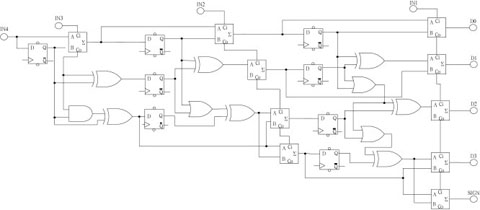

首先构建一个4级pascal三角形电路,其中CLOCK是时钟信号,IN1、IN2、IN3、IN4分别对应于pascal三角形的前4行,CLEAR是清零信号。IN1、IN2、IN3、IN4输入之前将触发器清零,防止输出不定态。D0、D1、D2、D3是从低到高的四位输出,SIGN是符号位,这五位构成输出。值得注意的是,IN4经过与自己直接相连的D触发器产生的数只有一位,然而它的补码需要4位,只好在高位加零,这样补码电路就可以简化,图7就是经过简化的电路图。为了增加电路的直观性,这里省略了电路中所有D触发器的时钟信号和清零信号,所有D触发器的清零信号和时钟信号分别连在一起。

图7 pascal三角形实现电路 真值表

| IN4 |