关键词:高速;流水线;FLASH;FPGA

0 引言

在数据采集存储系统中,往往需要对采集后的数据进行存储以方便后续分析处理。随着我国航空电子技术和雷达成像技术的快速发展,分辨率和采样率大幅提升,由此便带来了高速大容量数据的存储问题。同时存储系统又要求掉电存储数据并具有良好的抗振动能力,因此存储电路通常采用非易失的电路芯片构成,而传统的DOC,E2PROM等存储技术由于容量小、速度低等缺点已经不适用高速大容量数据的存储。快速发展的闪速存储器(FLASH MEMORY)因其具有体积小、成本低、功耗小、寿命长、抗振动和宽温度适应范围等特点,逐渐成为高速大容量存储系统设计的主流方案。

1 FLASH的控制逻辑

目前FLASH芯片主要分为NOR型和NAND型。NOR型具有可靠性高,随机读取速度快等优点,适用于程序代码的存储。NAND型是一种线性存储设备,适用于大容量数据和文件的存储。 K9WBG08U1M是三星公司推出的一款NAND型FLASH芯片,存储容量达到4 GB,它内部由两片2 GB的FLASH构成,通过片选信号CE1/CE2进行选择控制,每片FLASH由8 192个块组成,每块有64页,每页能存储(4 096+128)个字节的数据。因此,访问芯片需要5个地址周期,其中3个周期的行地址用来确定某一页,2个周期的列地址用来确定每页的某个字节。对FLASH进行的操作主要有:存储、读取和擦除。由于指令、地址和数据复用芯片的8个I/O口,因此需要2个控制信号CLE和ALE分别锁存指令和地址。

存储操作一般使用基于页的连续存储模式,所有的命令字、地址、数据都是在

读取操作通常也以页为单位进行。输入起始命令字00H、5个周期的地址和结束命令字30H后,对应地址的一页4 096个字节数据便传输给数据寄存器,随后在

擦除操作与存储、读取操作略有不同,它是以块为单位进行的,因此只需要3个周期的地址即可。在输入擦除命令后,芯片便自动进行擦除操作,将存储体内的数据全部恢复为“FF"状态,随后也可通过输入读状态命令字70H判断端口输出是否为0来检测此次擦除操作的成功性。

2 系统存储关键技术

K9WBG08U1M一页的存储容量是4KB,最短25ns时间写入一个字节。因此,芯片接口的写入速度最高为40MB/s。芯片的存储时间分为加载时间和编程时间两部分,写满一页所需的命令、地址和数据的加载时间总共为102.5μs,编程时间的典型值为200μs,最大编程时间为700μ-s。为了减小数据在存储过程中出错的概率,设计中使用最大的编程时间进行计算,因此对单片FLASH而言,存储速度最高可达5.1MB/s。

2.1 并行总线处理技术

按照操作FLASH的传统方法,存储完一片FLASH后,再进行下一片FLASH的操作,这样最高存储速度也只是单片FLASH的存储速度即5.1 MB/s,显然无法适用于高速数据传输存储的场合。通过并行处理技术可以很直观的提高存储速度,具体实现方法是:将N片低速FLASH芯片并联起来,使用相同的控制线、片选线和读写信号线,构成一个多位宽的FLASH组。这样N片FLASH并行工作,进行相同的操作,存储量可达到单片FLASH的N倍,所以理论上存储速度也是单片FLASH的N倍。

2.2 流水线技术

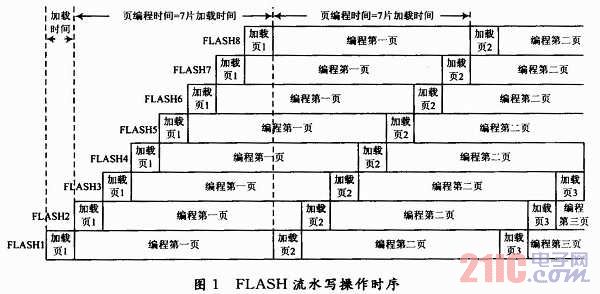

流水线技术在计算机领域得到广泛运用,它是在程序执行时多条指令重叠进行操作的一种准并行处理实现技术。借鉴这种技术在进行FLASH存储时可以大大节省存储时间,提高存储速度。FLASH每页数据的加载时间和编程时间是器件本身所决定的,当加载完一页数据后,FLASH就进入忙状态,此时需要等待加载的数据自动编程,即将数据从寄存器中写入存储单元内,这期间不能进行其余的操作,当编程结束后,FLASH才恢复空闲状态,此后才能进行下一页数据的加载,然后再进行编程。因此如果可以善加利用编程时间,使FLASH在进行本页数据编程的同时去执行下一页数据的加载,这样便可节省存储时间,提高速度。加载完一页数据的时间约为102.5μs,最大编程时间为700μs,这样在每页的编程时间内可以完成7次的FLASH加载操作(700/102.5≈7),由此画出8级流水操作的时序图如图1所示。

图1中每片FLASH都分为加载时间和编程时间,当第一片FLASH完成第一页的数据加载后进入数据编程阶段。此时第二片FLASH开始进行第一页数据加载,加载完成后也进入数据编程阶段。然后依次对第三片到第八片FLASH进行相同的操作,当第八片FLASH也完成了第一页数据的加载后,此时系统耗费的总时间约为7×102.5=717.5μs,大于单片FLASH的最大编程时间700μs即第一片FLASH已经完成了数据编程,可以接着进行第二页的数据加载。当第二页数据加载完成后,第三片FLASH便完成了第一页的数据编程,可以接着进行随后操作。这种循环流水操作,使FLASH在高速存储过程中不必去考虑页编程是否完成,节省了页编程时间,从而使存储速度近似达到芯片接口写入速度即40 MB/s。由此可见,运用流水操作技术的存储速度将是单片FLASH存储速度的8倍,实现了FLASH的快速高效无丢失存储。

2.3 坏块处理技术

NAND型FLASH芯片在出厂时内部会随机分布有坏块,坏块是指一个块内含有一位或更多位的数据单元无法进行操作,并且在芯片的长期使用过程中不可避免地还会增加新的坏块。不允许对坏块进行擦除和编程操作,这样会导致数据的存储错误。因此在操作FLASH的过程中,需要建立一个坏块管理列表,将芯片内部的所有坏块信息写入列表中,并且在出现新的坏快时能够及时的更新坏块管理列表。

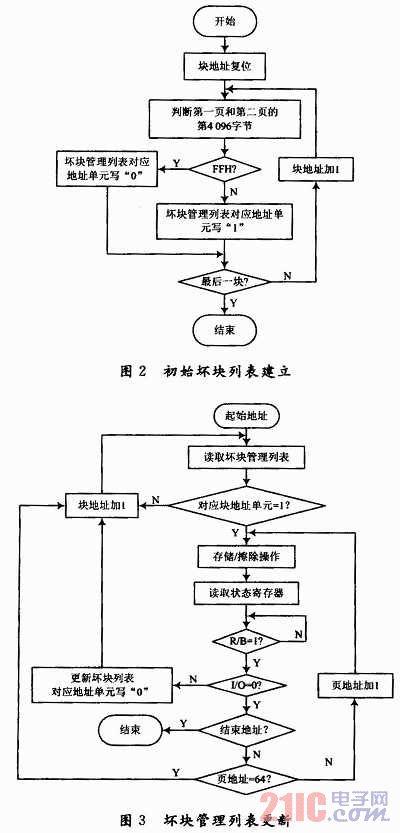

FLASH内部的坏块有两种,一种是芯片出厂时本身含有的初始坏块,此类坏块厂家已经标明,通过读取芯片每块第一页和第二页的第4 096个字节来进行判断,如果均是“FFH”,则认为此块是有效块,否则便为坏块。另一种则是在使用过程中新增加的坏块,可以通过读状态寄存器来进行判断。

坏块管理列表的建立和更新可以使用将其内部地址空间和FLASH内部块地址一一对应的映射方法,当发现是坏块时,只需将列表中对应此块地址的单元写入1比特“0”信息即可,而其余的地址单元仍是1比特“1”信息代表有效块。在对FLASH的每一块进行操作之前,需要先读取坏块管理列表中对应此块地址单元的信息,如果发现是坏块就跳过此块不进行操作,然后再进行下一块的判断,直至找到有效块时再进行操作。坏块管理列表的建立和更新分别如图2、图3所示。

3 系统设计

3.1 系统硬件结构组成

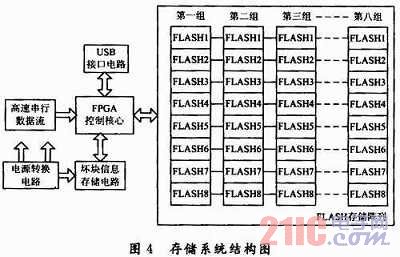

本文所设计的高速大容量存储系统的结构框图如图4所示。系统中FLASH芯片选用三星公司的K9WBG08U1M,存储阵列分为8组,采用流水线操作,每组由8片FLASH并联共用控制线,各组对应行的FLASH共用数据线。系统存储容量达到4×8×8=256 GB,存储速度理论值为40MB/ s×8=320 MB/s。FPGA是整个系统的控制核心,它将产生各种复杂的逻辑时序来控制外围芯片协调有序地工作,选用Altera公司StratixⅡ系列的EP2S60F484I4芯片,该芯片有48 352个逻辑单元,内置存储RAM容量达2.5 MB,满足缓存数据的要求。USB接口电路选用CYPRESS公司的CY7C68013A,该芯片集成了一个8.5 KB片上RAM的8051核、4 KB的FIFO以及USB 2.0收发器,满足USB2.0通信协议,是进行USB2.0开发的常用芯片。坏块信息存储电路用于存储和更新FLASH存储阵列随机出现的坏块位置,它必须是非易失零出错的存储介质,因此选用AMD公司的Am29LV800B NOR型FLASH,存储容量为8 Mb,保证无坏块。

3.2 系统具体实现

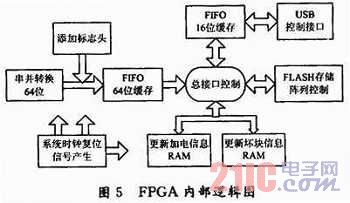

FPGA是整个硬件系统的核心,它完成电路的复杂时序控制,使系统有条不紊地运行。FPGA上电后进行初始化和加载配置信息,完成后进入工作状态。首先根据USB接口电压判断是进入数据记录状态还是数据下载状态,然后分别按照各自流程进行工作。FPGA内部逻辑设计如图5所示。

由于FLASH存储阵列是8片并联一起操作,因此数据总线宽度便为64位,同时由于USB的接口数据宽度为16位,因此系统中使用了2个FIFO分别进行缓存。在系统记录状态下,前端接收到高速串行数据后首先进行串/并转换,然后为其添加一个64位的标志头一并存入FIFO缓存,标识头是用来标记每次的加电情况,方便FLASH数据的分段下载。同时将外部NORFLASH内所存储的坏块信息读入FPGA内部建立的RAM中,在总接口控制下,屏蔽FLASH存储阵列内部的坏块,并按一定顺序将数据写入FLASH芯片。由于数据在存储过程中会产生新的坏块,因此在每页写操作结束后需判断此页编程是否成功,若编程失败,则对照此坏块地址更新RAM中的坏块信息,等待FLASH的存储操作结束后,再将更新后的RAM数据写入外部NOR FLASH进行保存。

在系统下载状态时,首先对FLASH内部的存储数据进行搜索,找到标识头所在存储阵列中的位置并将此位置信息写入FPGA内部的RAM中,这样便可知道每次加电后存储数据在FLASH阵列中的起始块位置和所占块的容量。然后通过上位机软件输入起始位置,块容量和下载命令后,FPGA内部的总接口控制便可根据这些命令信息,同时屏蔽坏块后将FLASH存储阵列中相应的数据写入16位FIFO缓存中,随后便可通过USB接口下载至计算机进行数据分析。

4 结语

随着基于NAND技术的FLASH固态存储器的快速发展,其存储密度也越来越大,而体积、功耗和成本却在减小,这使得NAND型FLASH在大容量高速存储设备的研制中得到广泛应用。本文针对单片FLASH存储速度慢的缺点,将多片低速FLASH芯片并行起来工作,同时又运用流水线操作节省了FLASH的自身编程时间,从而使得整个存储系统的存储速度大大提高。针对NAND FLASH内部存在坏块的问题,建立了一套完善的坏块处理机制,使得系统能够准确的存储数据,保证数据的可靠性。使用FPGA对FLASH存储阵列及USB下载电路进行控制,充分发挥了FPGA处理复杂逻辑的特点,简化了系统的硬件结构。