常见工业视频应用面临的难题 我们首先来检视一下几种常见的应用。机器视觉系统需要将捕获的图像数据从数码相机传输至远程帧捕获器。数据传输速率受图像捕获的分辨率、位深度及帧速率影响。设计较高的分辨率与位深度的图像,是为了提供进行复杂分析所需的细节数据。这对于因几何图形缩小而需要进行更精密检测的电子检查设备等应用至关重要。要提高整体的检查传送率,则需要更快的帧速率。 如今的机器视觉系统通常采用由 Camera Link 标准制定的通信接口。这个重要标准发表于 2000 年 10 月,多年来一直成功地为视觉行业提供支持。此接口由串行化数据(7:1 比率)的平行差动分对以及平行差动频率组成。图 1 所示为常见 Camera-Link 接口。

采用低电压差分信号传输 (LVDS) 的 7:1 串行方案,可为许多应用提供高效、强大的通信能力。但若将该技术扩展至较高吞吐量与较长距离,则存在一些限制和难题。当时钟速率提高和距离增长时,差分时钟与数据对的平行性质就容易受影响从而使配对之间的过长电缆发生偏斜。由于在相机链路的接收器端是使用独立时钟通道对数据进行采样的,因此保持正确的设置以及两者之间的关系非常重要。随着互连长度增加,对间偏斜也会增加,甚至可能会超过限制。为了将偏斜减至最小,可能需要高级且更贵的电缆与连接器。

在工业显示器系统中,影像来源(成像器或图形控制器)与数字显示器之间的链路也面临着类似的难题。如同视觉系统一样,工业显示器系统使用驱动器来提高数据速率,并且支持高达真彩色(每个像素 24 位)的较高色彩深度。更为明显的发展趋势是高清 (HD) 甚至更高分辨率的应用,这些影像可为监控及医疗应用提供有用的细节。平行 LVDS 解决方案(类似于 Camera Link 使用的解决方案)具有同样的电缆偏斜限制。随着数据速率提高,偏斜要求的限制会进一步减小,最大电缆长度也因此缩短。

使用嵌入式时钟接口可以消除配对之间的这种偏斜限制。所有数据与时钟经过编码和串行化后,将通过单一差分对进行传输。解串器接收串行流,然后使用时钟与数据恢复 (CDR) 电路提取时钟与数据信号。

采用低电压差分信号传输 (LVDS) 的 7:1 串行方案,可为许多应用提供高效、强大的通信能力。但若将该技术扩展至较高吞吐量与较长距离,则存在一些限制和难题。当时钟速率提高和距离增长时,差分时钟与数据对的平行性质就容易受影响从而使配对之间的过长电缆发生偏斜。由于在相机链路的接收器端是使用独立时钟通道对数据进行采样的,因此保持正确的设置以及两者之间的关系非常重要。随着互连长度增加,对间偏斜也会增加,甚至可能会超过限制。为了将偏斜减至最小,可能需要高级且更贵的电缆与连接器。

在工业显示器系统中,影像来源(成像器或图形控制器)与数字显示器之间的链路也面临着类似的难题。如同视觉系统一样,工业显示器系统使用驱动器来提高数据速率,并且支持高达真彩色(每个像素 24 位)的较高色彩深度。更为明显的发展趋势是高清 (HD) 甚至更高分辨率的应用,这些影像可为监控及医疗应用提供有用的细节。平行 LVDS 解决方案(类似于 Camera Link 使用的解决方案)具有同样的电缆偏斜限制。随着数据速率提高,偏斜要求的限制会进一步减小,最大电缆长度也因此缩短。

使用嵌入式时钟接口可以消除配对之间的这种偏斜限制。所有数据与时钟经过编码和串行化后,将通过单一差分对进行传输。解串器接收串行流,然后使用时钟与数据恢复 (CDR) 电路提取时钟与数据信号。

除了解决偏斜问题外,串行化解决方案还具有多个其它方面的优点。仅驱动一个差分对可减小互连媒体的整体大小。这意味着可以使用较小的电缆与连接器,将 PCB 上的连接器覆盖面积减至最小,并使接口变得更狭小且更具弹性。减少电缆组件中的配对数量,以及消除对严格偏斜容错的限制,将允许使用较低成本的电缆。

转移至串行化接口对系统设计具有非常积极的影响。但是,在使用嵌入式频率方案进行设计时,必须考虑一些因素。首先要考虑的是差动对上的数据速率现在比较高。过去通过四个配对来传输的数据,现在仅通过一个配对进行发送,因此数据速率大约提高了 4 倍。

简化设计的技术

除了解决偏斜问题外,串行化解决方案还具有多个其它方面的优点。仅驱动一个差分对可减小互连媒体的整体大小。这意味着可以使用较小的电缆与连接器,将 PCB 上的连接器覆盖面积减至最小,并使接口变得更狭小且更具弹性。减少电缆组件中的配对数量,以及消除对严格偏斜容错的限制,将允许使用较低成本的电缆。

转移至串行化接口对系统设计具有非常积极的影响。但是,在使用嵌入式频率方案进行设计时,必须考虑一些因素。首先要考虑的是差动对上的数据速率现在比较高。过去通过四个配对来传输的数据,现在仅通过一个配对进行发送,因此数据速率大约提高了 4 倍。

简化设计的技术 我们现在来探讨一下与较高接口速度相关的一些考虑因素,以及可用于简化设计和提供强大且具有成本效率的解决方案的各种功能与技术。

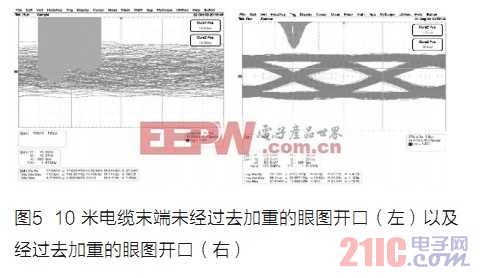

在这种较高的数据速率下,信号完整性显得尤为重要。我们将不再关注时钟与数据的一致性,而是关注串行化数据流内每个位的眼图开口。在数据穿越电缆时,信号会因衰减、抖动及符号间干扰 (ISI) 效应而降级。要正确接收信号,重要的是电缆末端(解串器输入端)的数据眼必须是“打开”状态。

电缆等化与去加重是专用于防止信号降级的两大功能。等化的作用是“重新开启”电缆最末端差动信号的数据眼。均衡器采用高通滤波器,以及与电缆衰减曲线成反比的增益曲线。可对均衡器增益进行编程的能力,允许通过不同电缆与长度来进行效能优化的微调。此电路可以是分离式电路,或是内置于解串器输入端。

第二项技术是信号波形还原,可防止符号间干扰 (ISI) 效应。依据正在传输的数据模式,电荷可能会累积在电缆上。这会妨碍快速切换至相反状态的能力。ISI 会导致信号振幅降低,这种情况在发送单一位(如由零组成的一个长字符串正中间的“一个”位)时尤为明显。此单一位转换的能量不足以抵消电缆上存储的电荷,因此在解串行器输入端的数据眼会呈现关闭状态。

在这种较高的数据速率下,信号完整性显得尤为重要。我们将不再关注时钟与数据的一致性,而是关注串行化数据流内每个位的眼图开口。在数据穿越电缆时,信号会因衰减、抖动及符号间干扰 (ISI) 效应而降级。要正确接收信号,重要的是电缆末端(解串器输入端)的数据眼必须是“打开”状态。

电缆等化与去加重是专用于防止信号降级的两大功能。等化的作用是“重新开启”电缆最末端差动信号的数据眼。均衡器采用高通滤波器,以及与电缆衰减曲线成反比的增益曲线。可对均衡器增益进行编程的能力,允许通过不同电缆与长度来进行效能优化的微调。此电路可以是分离式电路,或是内置于解串器输入端。

第二项技术是信号波形还原,可防止符号间干扰 (ISI) 效应。依据正在传输的数据模式,电荷可能会累积在电缆上。这会妨碍快速切换至相反状态的能力。ISI 会导致信号振幅降低,这种情况在发送单一位(如由零组成的一个长字符串正中间的“一个”位)时尤为明显。此单一位转换的能量不足以抵消电缆上存储的电荷,因此在解串行器输入端的数据眼会呈现关闭状态。

去加重可以在初始转换完成后,在线路上进行驱动的输出电压。这样就能将电缆上累积的电荷以及相关的直流偏移减至最少,使信号可以轻松转换为新状态。去加重的等级应该允许进行调整,以便针对互连特征优化效应。

EMI – 普遍问题

无论是使用传统接口还是使用串行化接口,所有系统都面临着一个共同的难题,那就是降低 EMI。随着分辨率与色彩深度提高,边缘速率与通道开关次数也会提高,从而导致电磁辐射增加。此问题可以从多方面解决,首先是从 LVDS 及其广泛用途着手。LVDS 使用通用平行视频接口(4 个数据对 + 1 个时钟对),并且还可用于串联化嵌入式频率解决方案。

但是,源与接收设备(帧捕获器或显示器)之间的连接可能使用 LVCMOS 接口。宽式平行 LVCMOS 输出总线是公认的辐射“热点”。请务必尝试将与这些输出开关相关的能量降至最低,并尽可能扩展此能量的频谱。由于平行输出切换更快,因此需要提高边缘速率。输出转换应该尽可能慢至能够有效支持要求的开关频率与输出负载。具有可程序化输出驱动的解串器可提供此弹性。

扩展能量的频谱是降低峰值辐射的常见做法。在某些情况下,源可能会提供扩频频率。所选串行器与解串器应该能够跟踪此频率调制以获得最大好处。在源进行扩展并非永远都能得到支持,因此还需要使用可自行生成扩频输出的解串联器,以便降低输出“热点”上的电磁辐射。

即使是使用具有降低 EMI 功能的芯片集,也务必要遵循合理的 印刷电路版设计惯例。

串行化视频的解决方案

美国国家半导体 Channel-Link II 系列的串行器/解串器芯片集,是专为简化串联化视频接口的应用而设计。75MHz 的最高时钟频率可支持 HD 720p 视频。高达 24 位的数据、附带的视频同步信号以及视频像素频率,经过串行化后将成为单一低电压差动输出。

这些芯片集均提供用于调整信号的可调式去加重与等化功能。

获得专利的直流平衡编码方案以及数据随机化和加密功能,可将 ISI 减至最少并降低链路上的辐射,从而扩展了频谱内容,否则这些未经扩展的频谱内容便会重复出现。串行器与解串器的设计,是要充分利用上游设备的扩频时钟,同时还提供自行生成的扩频时钟。降低 EMI 的其它功能包括降低驱动强度,以及交错开关平行输出驱动器。所有零件均提供“自动休眠”省电功能,当输入接口处于非活动状态时,便会切换至低功率模式。

平行总线可以与 LVCMOS 或 LVDS(4 个数据 + 1 个频率)连接。此 LVDS 接口相当于美国国家半导体的 28 位 Channel-Link 产品,并且提供简单易用的升级路径,其中的图像源、帧捕获器或显示控制器均包含集成 LVDS。

对于需要更高频宽与更长电缆驱动的系统,美国国家半导体的 FPGA-Link 解决方案则是理想选择。在接收设备和源上与具有成本效率的 FPGA 结合使用时,可通过 30 米长的电缆获得高达 3.125Gbps 的数据速率。解串器可提供重新定时的串行输出以驱动菊花链式接收设备,这在并排显示器应用中特别有用。

嵌入式视频系统可以获得使用串行化接口时所具有的性能与成本优势。可靠的设计惯例与技术,对于成功的实施非常重要。美国国家半导体的 Channel-Link II 与 FPGA-Link 芯片集,提供具有信号调整功能的串联化接口,可将偏斜问题降至最低,并允许使用更长且更细小的电缆。降低 EMI 的功能以及与各种来源和接收设备之间的兼容性,打造了简单易用且功能强大的解决方案。

去加重可以在初始转换完成后,在线路上进行驱动的输出电压。这样就能将电缆上累积的电荷以及相关的直流偏移减至最少,使信号可以轻松转换为新状态。去加重的等级应该允许进行调整,以便针对互连特征优化效应。

EMI – 普遍问题

无论是使用传统接口还是使用串行化接口,所有系统都面临着一个共同的难题,那就是降低 EMI。随着分辨率与色彩深度提高,边缘速率与通道开关次数也会提高,从而导致电磁辐射增加。此问题可以从多方面解决,首先是从 LVDS 及其广泛用途着手。LVDS 使用通用平行视频接口(4 个数据对 + 1 个时钟对),并且还可用于串联化嵌入式频率解决方案。

但是,源与接收设备(帧捕获器或显示器)之间的连接可能使用 LVCMOS 接口。宽式平行 LVCMOS 输出总线是公认的辐射“热点”。请务必尝试将与这些输出开关相关的能量降至最低,并尽可能扩展此能量的频谱。由于平行输出切换更快,因此需要提高边缘速率。输出转换应该尽可能慢至能够有效支持要求的开关频率与输出负载。具有可程序化输出驱动的解串器可提供此弹性。

扩展能量的频谱是降低峰值辐射的常见做法。在某些情况下,源可能会提供扩频频率。所选串行器与解串器应该能够跟踪此频率调制以获得最大好处。在源进行扩展并非永远都能得到支持,因此还需要使用可自行生成扩频输出的解串联器,以便降低输出“热点”上的电磁辐射。

即使是使用具有降低 EMI 功能的芯片集,也务必要遵循合理的 印刷电路版设计惯例。

串行化视频的解决方案

美国国家半导体 Channel-Link II 系列的串行器/解串器芯片集,是专为简化串联化视频接口的应用而设计。75MHz 的最高时钟频率可支持 HD 720p 视频。高达 24 位的数据、附带的视频同步信号以及视频像素频率,经过串行化后将成为单一低电压差动输出。

这些芯片集均提供用于调整信号的可调式去加重与等化功能。

获得专利的直流平衡编码方案以及数据随机化和加密功能,可将 ISI 减至最少并降低链路上的辐射,从而扩展了频谱内容,否则这些未经扩展的频谱内容便会重复出现。串行器与解串器的设计,是要充分利用上游设备的扩频时钟,同时还提供自行生成的扩频时钟。降低 EMI 的其它功能包括降低驱动强度,以及交错开关平行输出驱动器。所有零件均提供“自动休眠”省电功能,当输入接口处于非活动状态时,便会切换至低功率模式。

平行总线可以与 LVCMOS 或 LVDS(4 个数据 + 1 个频率)连接。此 LVDS 接口相当于美国国家半导体的 28 位 Channel-Link 产品,并且提供简单易用的升级路径,其中的图像源、帧捕获器或显示控制器均包含集成 LVDS。

对于需要更高频宽与更长电缆驱动的系统,美国国家半导体的 FPGA-Link 解决方案则是理想选择。在接收设备和源上与具有成本效率的 FPGA 结合使用时,可通过 30 米长的电缆获得高达 3.125Gbps 的数据速率。解串器可提供重新定时的串行输出以驱动菊花链式接收设备,这在并排显示器应用中特别有用。

嵌入式视频系统可以获得使用串行化接口时所具有的性能与成本优势。可靠的设计惯例与技术,对于成功的实施非常重要。美国国家半导体的 Channel-Link II 与 FPGA-Link 芯片集,提供具有信号调整功能的串联化接口,可将偏斜问题降至最低,并允许使用更长且更细小的电缆。降低 EMI 的功能以及与各种来源和接收设备之间的兼容性,打造了简单易用且功能强大的解决方案。