设计出色的低功耗应用需要同时考虑终端应用的需求和各种可用的 µC 特性。

设计人员可能会提出以下问题:是否能够重新充电?尺寸能够做到多小?典型的工作时间是多少?速度必须多快?要连接哪种类型的外围器件?这些答案将最终为确立设计标准和功率要求积累原始资料。

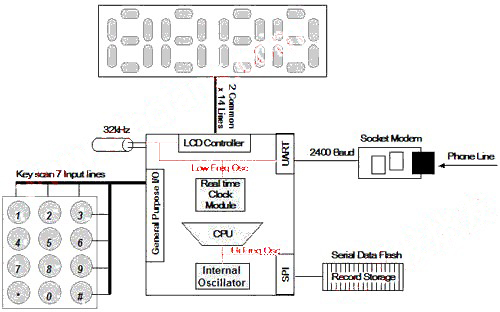

图 1:典型 µC 环境中的器件

处理功率

首先应该考虑 CPU 的处理功率,一般来说,CPU 是功耗最高的外围器件。处理器全速运行时,耗电量非常大,因此 CPU 处于待机或关闭状态的时间越多,电池寿命越长。例如,4 位处理器比 32 位处理器的功率消耗低;而处于休眠或停机状态的任何位数的处理器均比工作中的处理器的功耗要低。因此,如果 32 位处理器执行功能所耗的时间仅为 4 位处理器的1/10,那么,它在整个系统生命周期内要少消耗 9/10 的功率。因此,大多数制造商建议以较高的频率运行 CPU,迅速完成任务,并立即返回到功耗最低的休眠状态。总之,在选择处理器速度时,要考虑能够迅速处理预期工作量并尽可能长时间地处于休眠状态。

其次应考虑大多数便携式应用的中断服务例程 (ISR)。ISR 会定期唤醒处理器执行预排程序的或用户启动的任务,然后让处理器返回到休眠状态。进入和退出 ISR 所用的 CPU 时钟周期越少越好。事实上,许多 ISR(例如端口 I/O)有多个标志,这些标志可能会触发同一中断。采用程序计数器相对寻址方式的处理器会大大缩短识别和处理适当中断源所需的必要周期-尤其是在键盘扫描应用中。如果 ISR 编写得好,通过限制唤醒 CPU、执行任务和返回休眠状态所需的程序分支,可以确保处理时间最短。采用中断向量表的处理器中,程序计数器加载 ISR 地址,这种处理器有助于减少额外的程序分支,并降低功耗。自动上下文保存以及算术逻辑单元 (ALU) 标志和功率模式的恢复功能也可以促进节能。

此外,由于在低速或时钟停止的环境中,动态内核处理器不能保持数据的完整性,因而应尽可能使用静态内核处理器。

工作模式

休眠和“低功耗”模式也是必须考虑的重要问题。通过减慢唤醒时间实现低功耗状态(或关闭对唤醒器件非常重要的功能)会增加功耗,而不是降低功耗。

大多数低功耗器件的休眠或空闲模式会关闭处理器和时钟,通常流耗低于一微安。然后,需要 I/O 中断把处理器从休眠模式唤醒。使用 32kHz 时钟驱动定时器或实时时钟能以更灵活的方式唤醒处理器。基于32kHz 振荡器的功耗不像“深度睡眠”模式那样低,但它能以几微安的电流提供时钟功能。由于许多便携式应用需要实时时钟功能,这种改进可以让系统选用多种不同的外围器件。

需要注意的一点是,如果处理器必须使用 RESET 信号从停机状态唤醒,它必须运行所有硬件初始化程序。事实上,即使处理器SRAM 中的内容没有改变且仍然能够寻址中断,它也将不得不重新初始化处理器外围器件,这将消耗能量。

振荡器

在通过复位唤醒时,由于稳定振荡器晶体所花费的时间不同,内部振荡器能比外部振荡器多执行将近 1,000 条指令。例如,使用外部振荡器的100 MIP 机器启动、稳定和处理指令需要的时间为1 毫秒。与此相比,同一台机器仅需要1 微秒时间就可以使内部振荡器全速工作。让外部振荡器稳定的时间里,内部振荡器可以完成加电,执行 1000 条指令,然后恢复断电状态。这一时间通常已足够找到中断地址,并恢复断电状态。那么,为什么要考虑使用外部振荡器呢?外部振荡器通常在整个工作温度范围内更准确。事实上,在低功耗应用中,嵌入式程序装置经常习惯对照外部振荡器校准内部振荡器。这是因为驱动外部振荡器并使其达到速度所需的电路比内部振荡器消耗的功率更大。

选择内部振荡器时应慎重。虽然某些内部振荡器可以在数微秒内唤醒处理器,但是,必须在经过数毫秒,当外部晶体达到稳定之后, 才能以更高的速度运行,然后 CPU 时钟才能切换到更高的频率。例如,如果一个 100 MIP 的处理器有一个 20kHz 的内部时钟,该时钟与外部振荡器的 1 MHz 时钟同时启动,内部振荡器将仍然能够执行 999 条指令,而更高速度的处理器用同样的时间只能执行 20 条指令。

定时器

利用好定时器有助于在处理器保持待机状态的情况下实现系统处理功能。由于定时器功耗非常小,因此这有助于大大降低功耗。应该使用实时时钟模块接受 32kHz 计时器定时器输入和设置不同时间间隔的“警报”或中断,在无需处理器干预的情况下,使计时器计数增加。同样,应该使用影子寄存器更新和比较来自 ISR 的值。一旦寄存器读到有效的预编程值,即触发 ISR,使处理器脱离休眠或待机状态,而不需要 CPU 寻找 ISR 地址、更新周期或比较值。

管理开销

管理开销系统监视程序、监管工作有助于防范不安全的状况,有关器件包括电压监控器和看门狗定时器。由于数字电路依赖触发器或从负到正(或相反亦然)状态的转换,因此,即使工作电压有稍小的下降,也可能会意外触发 RESET 条件,从而造成系统无法工作。电力减弱保护作为电压监控的一部分,一般用于确保电压瞬变不会强制处理器进入和退出RESET 状态。

只要有可能,在电压监控解决方案中应采用不可屏蔽的中断 (NMI) 来识别电压瞬变。这种方法让用户能随心所欲地设定电压触发的门限电平,无需系统复位条件,其功耗一般比模拟-数字转换器 (ADC) 通道更低。

看门狗定时器监视故障情况。虽然在典型的嵌入式应用中,内嵌的系统程序器往往禁用看门狗定时器,但是在低功耗系统中,在电源电压不稳定的情况下,看门狗定时器是一种有用的工具。看门狗定时器会执行预先设定功能,例如在符合某些条件时,比如电压过低或有内存问题时,向处理器发出 RESET 指令。所选择的处理器应该能够生成已知的 ISR,使处理器无需执行 RESET 而恢复联机状态;因为执行 RESET,必须启动外围设备,因而会消耗更多的处理器功率。

UART 通信

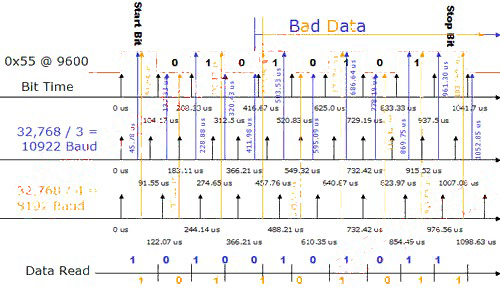

将一个数字时钟与另一个数字时钟精确到秒地同步是不可能的,因为每个时钟均与其内部晶体同步。在 MCU 驱动的系统中,低功耗模式下使用的 32kHz 实时时钟晶体与用于生成UART 波特率的普通 38.4kHz 频率之间会出现类似的同步问题。因为实时时钟的 32,768 频率使 15 位寄存器每秒溢出一次,所以非常适合时间保持(TIme-keeping) 应用。比较而言,在UART 中使用相同的频率,则在典型的 10 位(起始位、8 位数据和 1 个奇偶校验位)传输中保证至少有一位读取不正确。这是由于 32,768Hz 时钟必须除以 3.4,才能得到 9,600 波特率。由于没有 3.4 这一选择,因此必须选择除以 3 或除以 4(参见图2)。

将一个数字时钟与另一个数字时钟精确到秒地同步是不可能的,因为每个时钟均与其内部晶体同步。在 MCU 驱动的系统中,低功耗模式下使用的 32kHz 实时时钟晶体与用于生成UART 波特率的普通 38.4kHz 频率之间会出现类似的同步问题。因为实时时钟的 32,768 频率使 15 位寄存器每秒溢出一次,所以非常适合时间保持(time-keeping) 应用。比较而言,在UART 中使用相同的频率,则在典型的 10 位(起始位、8 位数据和 1 个奇偶校验位)传输中保证至少有一位读取不正确。这是由于 32,768Hz 时钟必须除以 3.4,才能得到 9,600 波特率。由于没有 3.4 这一选择,因此必须选择除以 3 或除以 4(参见图2)。

图 2:9600 波特传输时 32Khz 驱动 UART Rx 错误

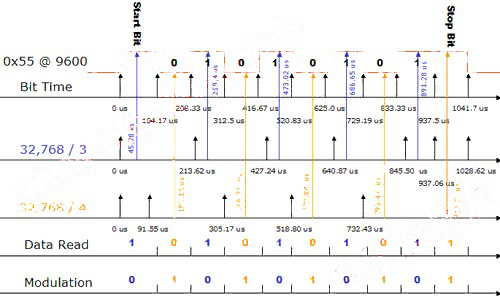

UART 数据用 10,922 波特或 8,192 波特的 UART 接收。由于 UART 在传输中间点对数据进行采样以补偿抖动,因此该点已经被选择为接收 UART 的采样点。在没有行抖动的理想情况下,10,922 波特 UART 对第三数据位的开始两次读数都会是错误的而8,192 波特的UART 由于会完全遗漏第三位,很快就将出错。由于低功耗应用的理想时钟是低功耗实时时钟模式,这使得在低功耗环境中处理很困难。解决这一问题的最好办法就是将 µC 与调制技术结合使用,用 32kHz 振荡器提供非常精确的 2,400 波特,并完全能支持9,600 波特(参见图 3)。

图 3:在 9600 波特传输时采用时钟调制的 32Khz 驱动 UART

通过混合两个时钟除数解决错误,总体积累的错误消失,数据接收正确。这种方法对于9,600 波特或以下的 UART 通信很有效。对于高速通信,几个 µC 监视 UART Rx 行的边缘跃迁并触发 ISR 启动内部高速振荡器,驱动 CPU 并处理中断。这使 µC UART 能够接收高速数据,而不必在 UART 空闲期间保持一个启动的高速时钟。如果使用外部振荡器或内部振荡器频率太低,则由于启动高速振荡器需要一定的时间,第一次传输将失效。为克服这一限制和效率损失,设计人员应该考虑使用能够唤醒并及时从 32kHz 或停机模式激活的处理器,从正在传输的 UART 恢复首次传输的数据。例如,系统时钟需要在 25µs 内启动,才能拾取起始位的中间点,从而正确接收 19,200 位的传输。

许多低功耗应用通过 UART 将 µC 连接到 RS-485 传感器网络。支持寻址和多处理器(9 位)模式的 UART 非常适合于这种网络。当第 9 位为 1(代表是一个地址)时,这些 UART 会生成一个 ISR,让处理器能够在其它传感器通过系统发送数据时保持休眠状态。某些 µC 会更进一步,在 UART 中加入地址匹配,仅在第 9 位是 1 且地址与在剩余 8 位中收到的数据匹配时才唤醒系统。

模拟器件

模拟器件模拟器件是最早的操作器件。模拟器件已经发展数十年,它是稳定电源、为高速晶体电路提供过滤和稳定性的必要器件,对监控来自自然界的输入信号也必不可少。

模拟器件模拟器件是最早的操作器件。模拟器件已经发展数十年,它是稳定电源、为高速晶体电路提供过滤和稳定性的必要器件,对监控来自自然界的输入信号也必不可少。

在待机模式下,模拟器件实际上不消耗功率。模拟-数字转换器 (ADC) 断电快,在待机模式下,甚至可以被视为一种低功耗应用。

一旦加电,缺点即暴露无遗。一般来说,模拟器件在工作时需要的电流很大。例如,ADC 工作时需要的电流达数百微安。另外,模拟器件(例如内部基准时钟)会使启动时间增加几毫秒,因为稳定模拟器件需要相对较大的外部电容。另一种经常被集成的器件-集成温度传感器-通常是随温度改变的二极管电路,也需要相当大的电流。

在低功耗应用中有几个需要考虑的标准。如果 ADC 有内部振荡器,就没有必要对其它系统振荡器加电来进行转换。在这种情况下,处理器保持断电状态,只有转换完成时起,才需要开始工作。像 CPU 一样,我们可以通过缩短执行时间来降低功耗。ADC 转换的速度越快,器件进入待机模式的速度越快。对于内部基准时钟也是这样。基准时钟启动和稳定得越快,转换完成和模拟系统断电的速度也越快。如果只是偶尔使用 ADC,某些处理器允许采样时钟断电,让跟踪电路保持加电。这样 ADC 就能够进入较浅的休眠模式。这种功能的负面影响是,在进行转换前,需要花较长时间来让采样和保持电路达到稳定。

转换完成之后,有几个 µC 集成了直接内存访问 (DMA) 或先入先出 (FIFO) 缓冲存储器,能够将多个转换存储在RAM 中,而无需唤醒处理器。在一定数量的转换到达之前,处理器会保持待机状态,而不是在每个转换后唤醒处理器来将数据移入 RAM,这样就可以降低功耗。

许多低功耗 µC 内置内部模拟比较器,可以执行简单的模拟任务。有些制造商的比较器允许编程,可以通过延长响应时间降低功耗。

起始点

总之,µC 外围设备的选择是由终端应用最终决定的,因此我们应从全面评估系统功能及其功率要求着手。许多处理器制造商宣称其器件具备低功耗工作能力,但是不同的应用对“低功耗”一词有不同的定义。是需要大量集成的速度更高的处理器,还是需要具有极深度睡眠模式的速度更低的处理器,更多地取决于内嵌系统的要求,而不是内嵌处理器所谓的“低功耗”工作能力。