1 EASY CORE的PLC芯片组

EASY CORE是一个加载了EASY嵌入式PLC软件平台的核心芯片组,用于设计PLC,其内部结构框图如图1所示。

1.1 EASY CORE内核

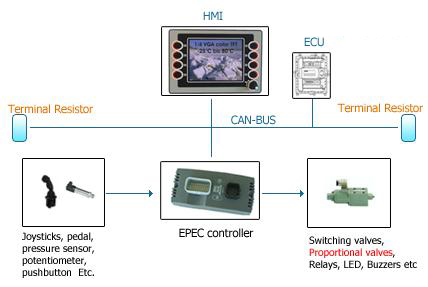

内核采用C8051F040混合式高性能单片机,片内有64个I/O端口引脚、1个CAN2.0B集成控制器、12位的ADC、PGA和模拟复用开关、2个12位DAC、64 KB的可编程Flash存储器、4 352(4 096+256)字节的RAM、SPI、SMBus/I2C、2个UART串行接口、5个16位通用定时器,可编程计数/定时阵列有6个捕捉/比较模块,片内有看门狗定时器、VDD监视器、温度传感器等,工业温度范围-45℃~+85℃内采用2.7~3.6 V的工作电压。

可通过设置开关交叉控制寄存器,将片内的计数器/定时器、串行总线、硬件中断、ADC转换启动输入、比较器输出以及微控制器内部的其他数字信号配置为在I/O引脚输出。允许用户根据自己特定的应用选择通用端口I/O和所需数字资源的组合。

内核采用实时操作系统,加载了与FX2N PLC兼容的梯形图语言的监控程序,指令系统与通信格式与FX2NPLC兼容。因而可以采用FX2N PLC软件编程,也可采用通用组态软件监控。

1.2 用户驱动开发接口

用户根据接口规范,可以嵌入完成特定功能的汇编程序,实现I/O点配置、AD/DA以及其他特殊的功能。

①嵌入程序代码存放地址为E000H~F7FFH。

②用户可使用的中断源如表1所列。

③位寄存器区中用户使用区(20H~23H)。

④直接寻址寄存器中用户使用区(58H~67H)。

⑤外部RAM中用户使用区(3600H~3FFFH)。

⑥PLC资源区(0000~5080H),系统程序和用户程序均可访问。位变量区和字变量区分别如表2、表3所列。

2 应用实例

现以8个输入点、7个输出点PLC设计为例,说明专用PLC的设计过程。

2.1 硬件电路设计

硬件电路由芯片组、电源电路、输入接口电路、输出接口电路、通信接口电路等组成。

2.1.1 EASY CORE芯片组外围引脚

EASY CORE芯片组引脚分布如图2所示。

(1)特殊用途引脚

P0.0,串口1的RXD,用于下载程序。

P0.1,串口1的TXD。

P0.2,串口2的RXD,用于RS4.85通信。

P0.3,串口2的TXD。

P4.5,PRO,嵌入式程序下载,低电平有效。

P4.4,RUN/SET。

CANRX、CANTXD,CAN总线接口。

(2)用户应用引脚

AIN0.0~AIN0.3,模拟量输入;

DAC0~DAC1,模拟量输出;

P1、P2、P3、P0.4~P0.7——数字I/O,可通过接口程序与

PLC的输入/输出缓冲区相连。

2.1.2输入/输出接口电路

输入接口电路:输入点为X0~X7(图中只画一条),输入接口采用光电隔离器TLP180,防止外界干扰,接口电路如图3所示。P3.0为高电平电压3.3 V。

输出接口电路:输出点为Y0~Y7(图中只画一条),输出信号经2003驱动输出继电器或晶体管,如图4所示。ULN2003AN为7路驱动器。

2.2 软件设计

PLC指令的解释、与上位机的通信等核心功能已由EASY CORE内核完成;用户程序只要根据接口规范,结合用户设计要求,编制少量的接口程序。

用户程序主要是把外部接口电路与内核软件的输入、输出缓冲区相联系。读P3.0~P3.7(X0~X7),送到相应RAM-PX,把RAM—PY(Y0~Y6)数据输出到P1.0~P1.6(Y0~Y6)。主要程序结构如图5所示。

(主要程序略——编者注)

3 结 论

基于芯片组的嵌入式PLC,能有效弥补通用PLC在低端市场的不足,与工艺对象结合紧密。只要解决好电路的抗干扰设计问题,嵌入式PLC有较大的市场前景。目前,笔者已将成功应用于龙门铣床的改造。