目前在很多地方的电信增值业务中,都包含了“语音邮箱”功能。在一些新型的终端设备(如一键通电话)上,已经集成了此功能,但大多数较早的电话机并不具备此功能,因此有客户要求开发一种简单的电话附加装置,以配合这些电话实现语音邮箱指示功能。

设计要求

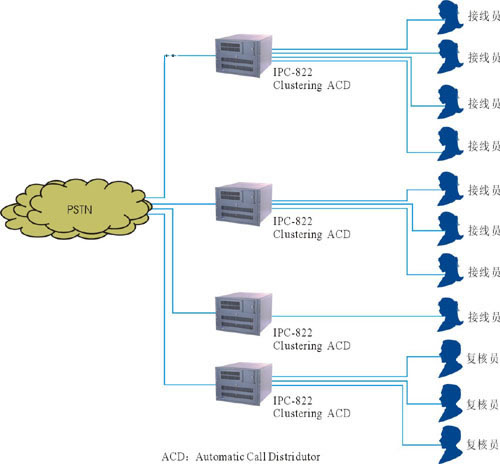

● 能正确区分并机(并机含义如图1所示)的取挂机状态。

图1 交换机、并机、语音邮箱指示盒三者连接关系

● 可以正确读出串行EEPROM中特定位置特定信义的数据。

● 在并机挂机状态可以接收各种制式与时序的来电显示,根据若来电的号码头部部分与EEPROM中预先设定的“语音邮箱提示码”完全匹配(即指若EEPROM中存储的邮箱提示码为1234,则收到所有以1234开头的号码均算匹配),则点亮一个LED(即语音邮箱指示灯),并使之按每2秒钟点100ms的规律闪烁。挂机时要有睡眠状态且打开line_det与IOC0中断唤醒,若需要点亮灯时可开2Hz中断唤醒,不须点亮灯时则不必。为安全起见不关32768晶振。收到的数据不必保存,比较完毕后就清除。

● 在并机取机状态能正确解调并机拨号。也就是说,在并机取机的时候系统能够正

● 并机取挂机状态突变时要重新收CALL解调。比如系统正在收CALL状态下,并机的状态突然改变,系统要能够跳出本次的收CALL操作并清除缓存区进行下一次收CALL。

考虑到可靠性,EEPROM中的数据应该在需要比较的时候去读取并比较,而不建议采取一上电就先读进缓存的做法。

其中,SPT6603A是一款最近推出的针对来电显示和语音拨号产品而专门设计的微处理器。line_det与IOC0是SPT6603A单片机专门为来电显示系统而设置的中断唤醒源。line_det用来检测线上的信号,IOC0用来检测极性反转信号。

电路分析

语音邮箱指示盒系统的原理与电话机系统的部分电路原理基本相同,在硬件电路上都包括了Caller ID输入回路、并机检测线路、阻抗匹配线路、防雷击与极性保护线路、CPU控制线路、EEPROM,只是电话机系统多了振铃线路、键盘拨号线路、LCD显示、手柄通话线路、免提通话线路、电子开关线路等。由于电话机系统的电路已经是非常成熟的电路,在硬件设计上面无须花很多的时间去设计各个单元电路,只需要调整电路的参数和加上指示灯就可以在硬件上实现语音邮箱指示盒的功能,于是语音邮箱指示盒系统就可以由电话机系统简化得来。语音邮箱指示盒系统原理框图如图2所示。

图2 系统原理框图

系统在设计的时候,修改EEPROM里面储存的号码如可以通过一台并机进行,如果不需要通过并机修改预存的号码,可以省去DTMF拨号部分。如果需要在指示盒上面修改EEPROM里面储存的号码,可以在这个系统上面加上键盘。 阻抗匹配电路主要是针对一些特殊的交换机而设计的,如果语音邮箱指示盒并联了一台具有来电显示功能的电话机,也可以不考虑这部分电路。

Caller ID输入回路的原理与分析

Caller ID可以根据实际场合给出相应的理解,如果用Caller ID修饰产品或者系统的时候就理解为来电显示;当用来修饰信号的时候就理解为主叫识别信息。Caller ID输入回路与CPU内部硬件解码器的原理图如图3所示。

图3 Caller ID输入回路与CPU内部硬件解码器的原理图

信号流程:在解码器打开时,图中的OP被Enable工作在线性状态,线上的Caller ID信号可以经过OP-C3-AGC然后解码。

唤醒过程:解码器关闭后,图3中的OP被Disable,输入端与之并联的比较器CMP因R1、R2、R3的存在而获得上低下高的偏置,CMP输出0。由于线路上极性保护电路的存在,T、R两端总有一脚处于交流低阻抗的状态,即可以认为交流信号是从其中某一端送来的。

对于有振铃触发的情况,在振铃期间,振铃的幅度足以使CMP发生反转,CMP输出1,程序上就做开解码器的动作。

对于直接送号的情况,比如R2上分得的电压是0.15V,若T或R上送来的信号的峰值超过了0.15V,则该信号也可以克服预加在CMP输入端的偏置电压,从而引起CMP反转,进而唤醒CPU解码。

对于有反极性触发的情况,若是从T- R+反转到T+ R-,则相当于T端升高,R端降低。此一升

一降加到CMP的输入脚以后,正好使CMP反转,从而可以唤醒CPU收CALL;若是从T+ R-反转到T- R+,则相当于T端降低,R端升高。因为对于CMP而言本身T端对应的输入脚就较R端要低,所以本次反极性不能造成CMP的反转。C5、R6、R7组成的电路正是为解决这一问题而设置的。当T端迅速降低时,会有一个负向的脉冲在RIN引脚产生,此脉冲可以唤醒CPU收CALL。并机检测线路的原理与分析

并机检测的意义如下。

● 在系统收CALL的时候判断并机取挂机状态可以知道接收的信号是来自交换机还是并机的拨号;

● 在并机取机的过程中,为了省电本机要跑相对低功耗的模式;

● 为了实现防盗功能,系统必须加上并机检测线路。

并机检测的实现方法:在并机挂机的状态下,DM引脚为高,当并机取机的时候DM引脚变为低电平,由这种跳变系统就可以准确的区分并机的取挂机状态。值得注意的是当本机取机的时候,无论并机取机还是挂机,DM引脚始终为低,也就是说在本机取机的时候,并机检测是无效的。并机检测线路原理图如图4所示。

图4 并机检测线路原理图

结束语

实现语音邮箱指示盒功能的整个硬件