当采用现场可编程门阵列(FPGA)进行设计时,电源排序是需要考虑的一个重要的方面。通常情况下,FPGA 供应商都规定了电源排序要求,因为一个FPGA所需要的电源轨数量会从 3 个到 10 个以上不等。

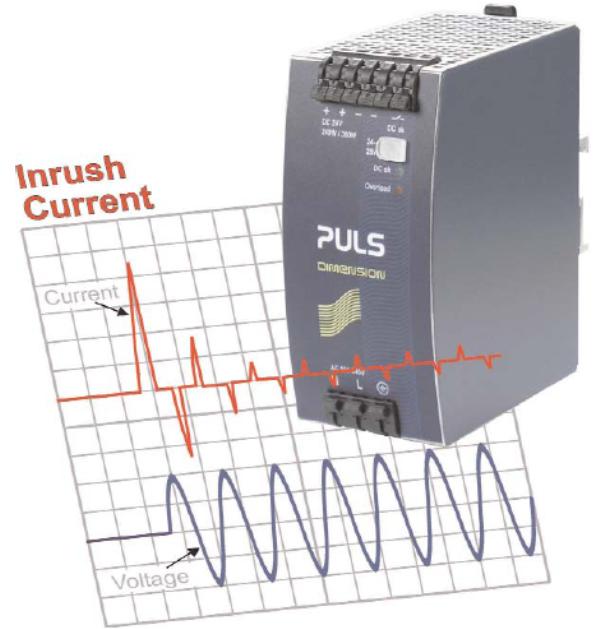

通过遵循推荐的电源序列,可以避免在启动期间吸取过大的电流,这反过来又可防止器件受损。对一个系统中的电源进行排序可采用多种方法来完成。本文将详细说明可根据系统所要求的复杂程度来实现的电源排序解决方案。

本文中所讨论的电源排序解决方案为:

1. 把 PGOOD 引脚级联至使能引脚;

2. 采用一个复位 IC 来实现排序;

3. 模拟上电 / 断电排序器;

4. 具有 PMBus 接口的数字系统健康状况监视器。

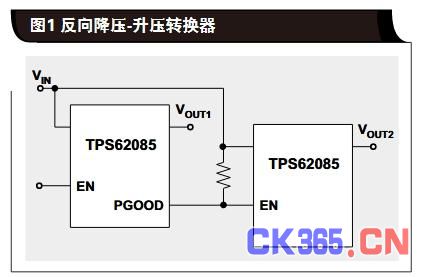

方法一:把PGOOD 引脚级联至使能引脚

实现排序的一种基本的成本效益型方法是把一个电源的电源良好PG)引脚级联至相继的下一个电源的使能(EN) 引脚。

第二个电源在 PG 门限得到满足(通常是在电源达到其终值的90% 之时)时开始接通。这种方法的优势是成本低,但是无法轻松地控制定时。在EN 引脚上增设一个电容器会在电路级之间引入定时延迟。然而,此方法在温度变化和反复电源循环期间是不可靠的。而且,这种方法并不支持断电排序。

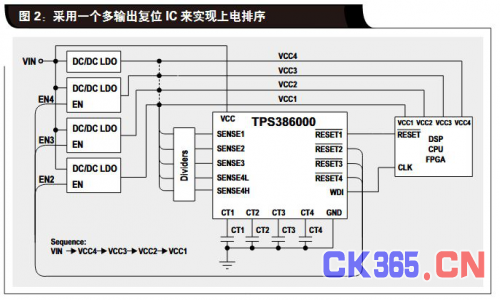

方法二:采用一个复位 IC 来实现排序

另一种可以考虑的用于上电排序的简单选项是采用一个具有时间延迟的复位 IC。当采用此选项时,复位 IC 以严格的门限限值来监视电源轨。一旦电源轨处于其终值的3%(或更小)以内,复位 IC 将进入由解决方案定义的等待周期,然后再执行下一个电源轨的上电操作。该等待周期可以采用 EEPROM 编程到复位 IC ?中,也可利用外部电容器来设定。图 2 示出了一款典型的多通道复位IC。采用复位IC 来实现上电排序的优点是解决方案处于受监视的状态。

必须在确认每个电源轨都处在稳压范围内之后再释放下一个电源轨,而且无需在电源转换器上提供一个PGOOD 引脚。采用复位 IC 的电源排序解决方案的缺点是其并不实施断电排序。

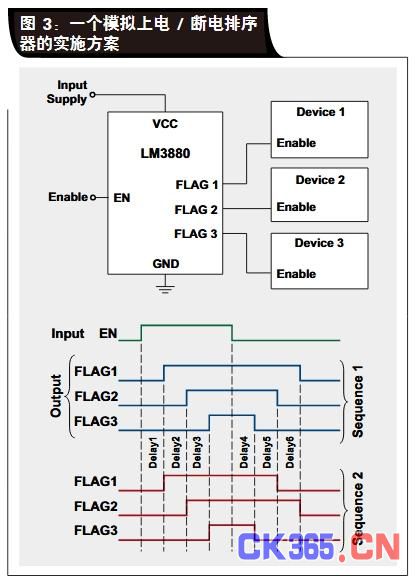

方法三:模拟上电 / 断电排序器

实施上电排序会比实施断电排序更加容易。为了实现上电和断电排序,人们推出了能够相对于上电序列进行断电序列的逆转(序列 1)乃至混合(序列 2)的简单模拟排序器。

在上电时,所有的标记均保持在低电平,直到EN 被拉至高电平为止。在 EN 被置为有效之后,每个标记于一个内部定时器计时结束后顺序地变至漏极开路状态(需要上拉电阻器)。断电序列与上电序列相同,但次序正好相反。

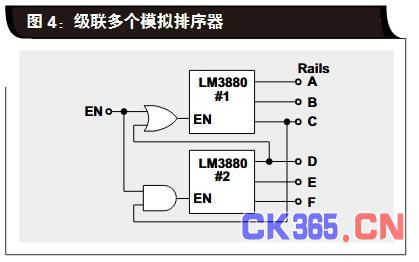

可以把排序器级联在一起以支持多个电源轨,并在使能信号之间提供固定和可调的延迟时间。在图? 4 ?中,两个排序器级联在一起以实现 6 个有序的电源轨。上电时,AND 门确保第二个排序器在其接收到一个 EN信号且? C ?电源轨被触发之前不被触发。

断电时,AND 门确保第二个排序器承受EN 下降沿,而不考虑 C输出。OR 门确保第一个排序器由 EN 上升沿来触发。断电时,OR 门确保第一个排序器不能承受 EN 下降沿,直到D电源轨下降为止。这保证了上电和断电排序,但并未提供一个受监视的序列。

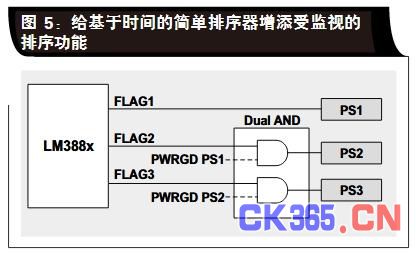

如图5 所示,通过简单地在 FlagX输出和? PG ?引脚之间增设几个 AND 门,就能给图 4 中的电路添加受监视的排序功能。在该例中,PS2 仅在PS1超过其终值的90% 的情况下使能。这种方法可提供一种低成本、受监视的排序解决方案。