功率MOSFET的失效机制主要分为以下几类:

ElectroStaticDischarge (ESD) - 静电放电

Avalanche 击穿 - 雪崩击穿

超出SOA(Safe Of Area)or ASO(Area of Safe Operation)- 超出安全工作区

内部寄生二极管击穿

一)静电放电

静电放电是指产品在制造、运输与安装过程中,如果处理不当,产品会受到静电放电或者浪涌电压的冲击,从而造成产品的损伤或者破坏。

静电放电对MOSFET的危害通常来自于放电电压对于MOSFET驱动极的冲击和破坏。驱动极如果遭到破坏,通常会表现为MOSFET驱动极与源极短路,耐压跌落或者漏电流增加等。

对于静电放电通常有以下几种应对措施。

二)Avalanche(雪崩)击穿

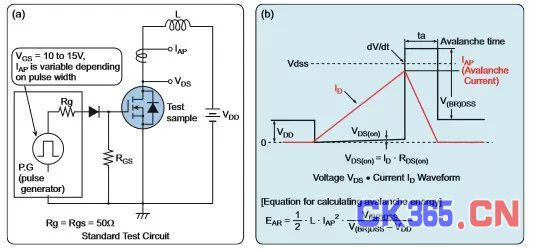

1. Avalanche 测试线路

2. Avalanche 雪崩电流和能量

3. Avalanche 击穿应对措施

三)超出SOA工作安全区

MOSFET的SOA(安全工作区)已在本公众号“MOSFET应用参数理论详解”一文中进行了详细介绍,本篇不再赘述。

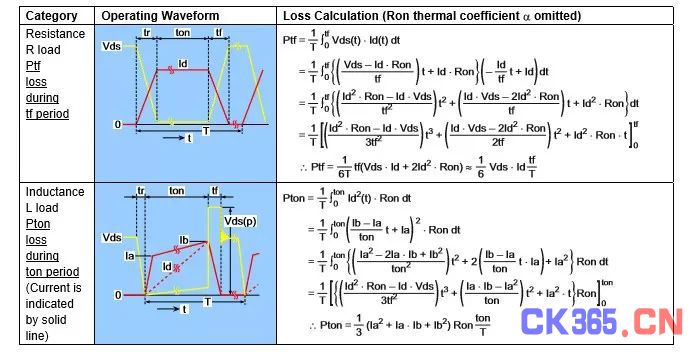

1. Power MOSFET 损耗计算

2. Power MOSFET损耗计算举例

3. 超出SOA或者ASO工作区的应对措施

四)内部寄生二极管失效

1. Power MOSFET的内部结构和等效电路

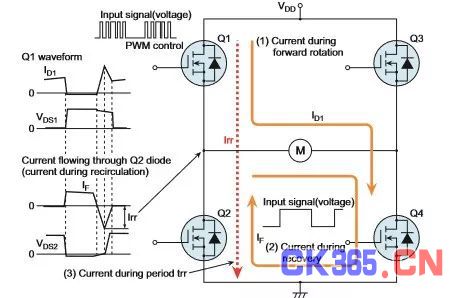

2. 全桥线路举例,二极管失效通常发生在内部二极管反向恢复时间内

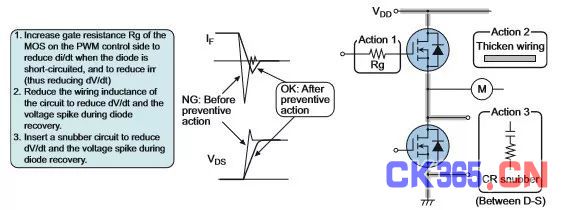

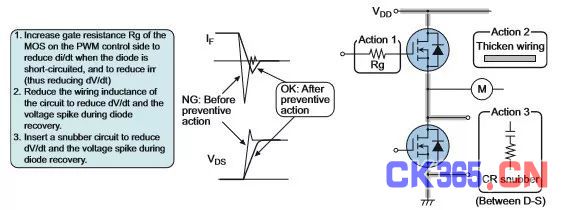

3. 内部二极管击穿应对措施

五)MOSFET击穿后芯片不同表现