FPGA(Field-Programmable Gate Array),即现场可编程门阵列,它是作为专用集成电路(ASIC)领域中的一种半定制电路而出现的,既解决了定制电路的不足,又克服了原有可编程器件门电路数有限的缺点。对于时序如何用FPGA来分析与设计,本文将详细介绍。

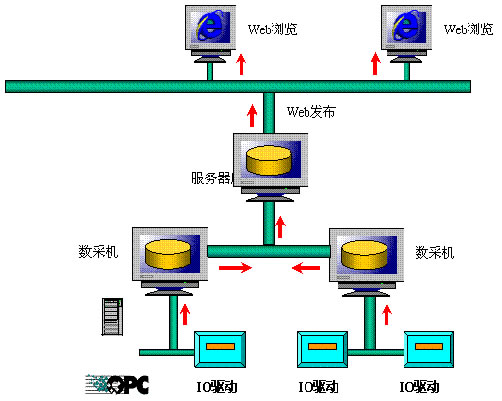

基本的电子系统如图 1所示,一般自己的设计都需要时序分析,如图 1所示的Design,上部分为时序组合逻辑,下部分只有组合逻辑。而对其进行时序分析时,一般都以时钟为参考的,因此一般主要分析上半部分。在进行时序分析之前,需要了解时序分析的一些基本概念,如时钟抖动、时钟偏斜(Tskew)、建立时间(Tsu)、保持时间(Th)等。时序分析也就是分析每一个触发器(寄存器)是否满足建立时间/保持时间,而时序的设计的实质就是满足每一个触发器的建立时间/保持时间的要求。

图 1 基本的电子系统

一、时钟抖动和时钟偏斜

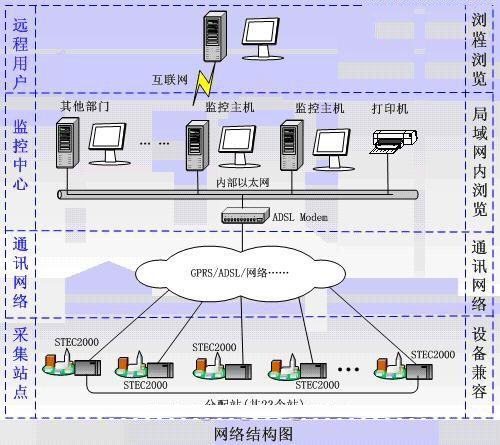

1.时钟抖动

时钟信号边沿变化的不确定时间称为时钟抖动,如图 2所示。一般情况下的时序分析是不考虑时钟抖动,如果考虑时钟抖动,则建立时间应该是Tsu+T1,保持时间应该是Th+T2。

图 2 时钟抖动时序图

2.时钟偏斜

时序偏斜分析图如图 3所示。时钟的分析起点是源寄存器(Reg1),终点是目标寄存器(Reg2)。时钟在图中的结构中传输也会有延迟,时钟信号从时钟源传输到源寄存器的延时为Tc2s,传输到目标寄存器的延时为Tc2d。时钟网络的延时为Tc2s与Tc2d之差,即Tskew=Tc2d-Tc2s。

图 3 时钟偏斜时序图

二、建立时间和保持时间

建立时间(Setup Time)常用Tsu表示,指的是在触发器的时钟信号上升沿到来以前,数据和使能信号稳定不变的时间,如果建立时间不够,数据将不能在这个时钟上升沿被打入触发器,使能信号无效,也就是说在这个时钟周期对数据的操作时无效的;保持时间(Hold Time)常用Th表示,指的是在触发器的时钟信号上升沿到来以后,数据和使能信号稳定不变的时间,如果保持时间不够,数据同样不能被打入触发器,对数据的操作同样是无效的,使能信号无效。数据要能稳定传输,就必须满足建立时间和保持时间的关系,图 4标识了它们间的关系。

图 4 建立时间/操持时间的概念

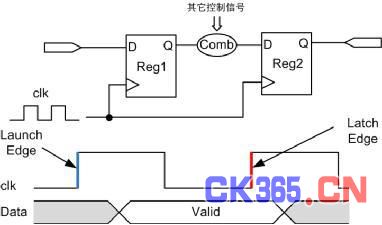

三、发送沿和捕获沿

(1)发送沿(Launch Edge):前级寄存器发送数据对应的时钟沿,是时序分析的起点;

(2)捕获沿(Latch Edge):后记寄存器捕获数据对应的时钟沿,是时序分析的终点。相对于launch Edge通常为一个时钟周期,但不绝对,如多周期。

“信号跳变抵达窗口”:对latch寄存器来说,从previous时钟对应的Hold Time开始,到current 时钟对应的Setup Time 结束。

“信号电平采样窗口”:对latch寄存器来说,从current时钟对应的Setup Time开始,到current时钟对应的Hold Time结束。

launch寄存器必须保证驱动的信号跳变到达latch寄存器的时刻处于“信号跳变抵达窗口”内,才能保证不破坏latch寄存器的“信号电平采样窗口”。

图 5 Launch Edge和Latch Edge