ADI推出GSPS数据转换器拯救电子监控与对抗系统

频谱拥堵、更高工作频率和更复杂的波形,给电子监控与对抗系统带来层出不穷的问题,需要侦测的带宽越来越大,检测灵敏度要求也越来越高。随着越来越多的功能通过数字域实现,上述带宽和灵敏度两个因素,加上成本,直接把高速模数转换器(ADC)的性能推向极限,常常使ADC成为系统的局限所在。所幸的是,新一代高速ADC的性能水平符合要求,可提供一些系统级解决方案来应对这些挑战。

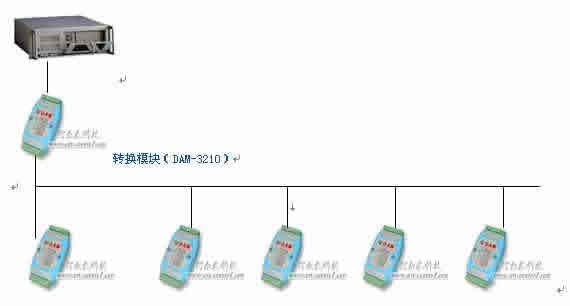

现代监控系统的架构如图1所示,它包括三个基本功能:

●射频/微波调谐器

●数字化仪,ADC及相关的放大器和缓冲器

●快速傅里叶变换和数字信号处理

很多情况下,高速ADC性能——从模拟域到数字域的转换——成为系统的限制因素。尽管最大限度降低成本和系统尺寸始终极其重要,但系统设计人员还必须关注如何最佳地平衡提高瞬时监控带宽的需求(以便最大限度提高拦截概率),以及如何将带内高功率信号降低系统灵敏度的影响减至最少。

表1:高线性度低速ADC与过去和现在的GSPS ADC的对比

关于如何达到系统指标和已确定的取舍要求,ADC的采样速率和无杂散动态范围(SFDR)通常是影响决策的两大主要因素。转换器的采样速率决定奈奎斯特频段,进而决定个别转换器的最大可观测带宽;SFDR决定可检测的信号电平。虽然噪声频谱密度可能也需要考虑,但在多数情况下,ADC的噪底远低于杂散水平,而且从系统运行角度看,数字化过程中产生的杂散与频谱中进行数字化的低功率信号难以区分。因此,系统的灵敏度与SFDR直接相关,这样检测到假目标的可能性最低。

例如,考虑对两个连续波(CW)信号进行数字化处理,信号A是一个满量程输入,信号B的功率则低得多。作为目标信号的信号B与数字化信号A所产生的杂散可能难以区别,因为二者的电平相似。所以,信号B可能低于系统的检测电平,不会被标示为目标信号。

图1:监控系统基本架构

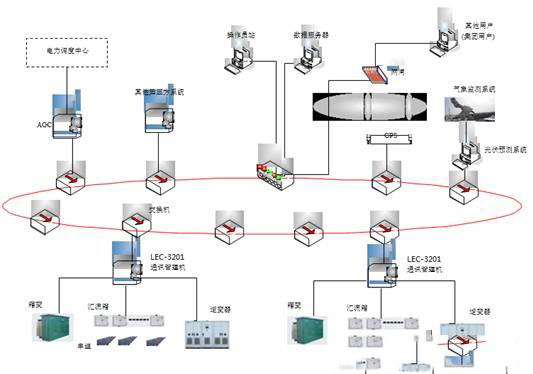

诸如此类的限制表明:利用具有超高线性度的ADC可实现最佳检测电平,但高线性度传统上是通过牺牲ADC采样速率来实现的。为了方便讨论,本文考虑一个通用电子监控系统,但类似的系统架构权衡也适用于电子情报(ELINT)、信号情报(SIGINT)和通信情报(COMINT)。此类系统一般有三种不同系统架构可供考虑(参见图2)。

图2A所示为最简单的系统。采用高线性度ADC,例如ADI公司的AD9265(其在70 MHz中频输入时具有93 dBc的SFDR和79 dBFS的信噪比(SNR),这种架构可提供出色的灵敏度和检测性能,但最大采样速率只有125 MSPS.这是以瞬时带宽为代价而获得的,不考虑抗混叠滤波器时的最大瞬时带宽为62.5 MHz,通常要降低到40 MHz或更低。系统中只有一个转换器,系统成本很低,但射频调谐器不得不以40 MHz的步幅扫描整个射频带宽,这会降低拦截某些信号的概率。

为了提高带宽,一种显而易见的方法是交错使用多个高线性度、低采样速率的转换器,将其连接到单个宽带射频调谐器(图2B),从而提高有效采样速率和瞬时带宽。例如,若交错使用8个AD9265 ADC,总有效采样速率将达到1 GSPS,支持的瞬时带宽接近500 MHz.射频调谐器只需以500 MHz的步幅扫描,因此射频频谱的侦测速度会快得多,拦截目标信号(尤其是捷变信号)的概率更高。另外,系统仅使用一个射频调谐器,与图2A相比,成本增加有限。

虽然这确实给射频调谐器带来更多难题(更宽的带宽带来的难题是要保持与前述架构相似的IP3和噪声性能),但这种方法的主要不足是交错ADC方面。各转换器在增益、直流失调和相位方面的失配,需要通过校准从系统中消除或利用数字信号处理加以管理,但即便这样,SFDR、噪底或带宽通常也会有一定的下降,导致此架构性能降低。对于监控带宽内的超高功率信号,系统可能不太敏感,使问题进一步恶化。500 MHz频段任意地方的这种信号都要求降低射频和中频增益,从而限制了低功率信号的拦截概率。

最高性能的架构如图2C所示,其中实现了多个并行射频与数字化仪子系统,如果同样使用AD9265,则可以同时观测到多个相邻40MHz频段。让每个子系统偏移大约40 MHz(需要一些交叠),可以提高瞬时带宽,但很显然,这是以系统成本为代价,系统成本与瞬时带宽成正比。与交错方法相比,这种架构的好处是无需通过校准或数字信号处理来消除交错引起的杂散。此外,该系统抑制高功率阻塞或干扰的能力更强,因为各40 MHz频段的射频/中频增益可以独立设置。

图2:监控系统架构选项

上述系统架构已在当今各种系统中采用,但如图中所示,每种架构在性能、成本,还有可能是尺寸上存在限制。然而,最新的GSPS ADC可能很快就会打破现状,这种ADC具备更高的线性度和嵌入式数字信号处理特性。AD9625和AD9680等新型ADC提供1.25 GSPS到2.5 GSPS的采样速率,SFDR高达85 dBc.

GSPS ADC的线性度比不上低采样速率的器件,但可以看出,差距正在缩小。使用单个GSPS ADC就能实现图2B所示的架构,同时不会有交错带来的缺点。此外,更高的线性度可提高检测灵敏度,并将干扰和阻塞的影响降至最小,缩小这种架构与图2中图2C所示系统的性能差距,而且成本更低,尺寸更小。

然而,虽然这一方面能促成新系统架构的出现,但这些新器件更激动人心的方面是它们还能在转换器的模数转换级之后实现数字信号处理功能。65 nm CMOS工艺支持在转换器中实现更高速度的数字信号处理。例如,AD9625和AD9680均实现了数字下变频(DDC)功能,因而高速ADC可动态改变带宽——从全带宽到1,000MHz以上的数字化奈奎斯特频段内的可选子频段。在图3所示的架构中,2.5 GSPS、12位ADC AD9625带有嵌入式DSP选项。

在宽带模式下,这种ADC支持以1GHz步幅监控射频频谱,以便快速评估射频图景。一旦确定目标信号,便可将此数据引导至DDC.DDC使用数字控制振荡器(NCO)和滤波级,可从转换器奈奎斯特频段内的任何地方选择一个频段,并进行8倍或16倍的数字抽取,从而进一步抑制噪底。虽然这一功能可以在器件中转换器之后的数字信号处理级中轻松实现,但在ADC本身中执行有助于降低ADC的输出数据速率,更重要的是,可以降低传输功耗。因此,使用DDC时,系统功耗显著降低。

图3:带可选且可旁路嵌入式数字下变频器的2.5GSPS ADC

航空航天和防务系统持续重视缩减尺寸、重量和功耗(SWaP),随着GSPS领域的高速转换器的线性度不断提高,系统架构师开始探索新的选项。把数字信号处理集成到高速转换器内部后,一系列选项和系统优化方法开始显露出来,现阶段因而成为新一代监控系统开发的一个令人兴奋的时期。