半导体行业目前面临集成电路(IC)制造方法的巨大变革,这一变革旨在不断提高IC的性能和密度,可能会对设计方法产生影响。晶圆代工厂家目前正准备根据finFET概念加强使用三维晶体管结构的14nm和16nm工艺,因为相比较20nm的平面型晶体管,它们可以提供更高的性能。

通过提高载流通道,可从门控的三面对其进行环绕,从而使门控展现出更强的静电控制。这克服了导致过多漏电流的短通道效应以及使用大量硅片制造的纳米平面型晶体管所产生的其他问题。

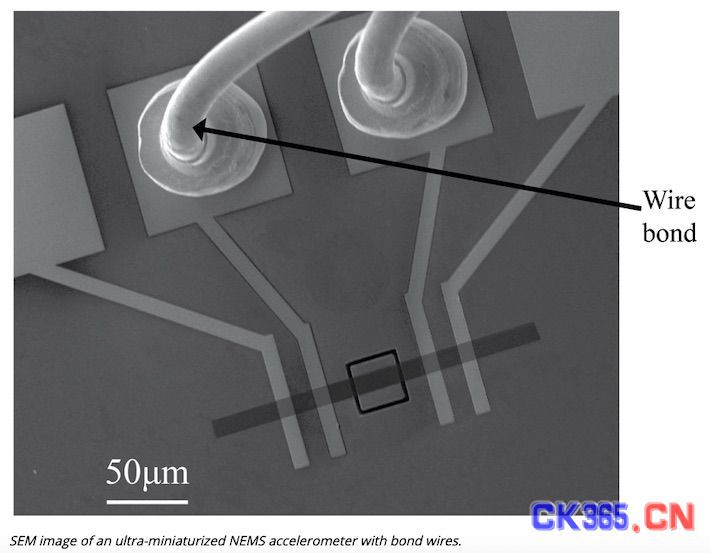

图1:更好地说明了频率范围内的漏电流控制

多层面门控的进一步优势在于单位范围内的驱动电流多于平面型器件单位范围内的驱动电流——相比于平面型器件,在等效门控长度相同的情况下,使用鳍(Fin)结构高度可创建有效容积更大的通道。这意味着有效性能更好。

通过增强FinFET性能,可在功率预算给定的情况下实现比体硅技术更高的频率数。功耗降低源于以下两个方面:对宽型高驱动标准单元的需求降低;以及漏电流量给定情况下,在较低电源电压下工作的能力。但是,只有改变设计技术才能完全实现功耗降低性能。

基于标准单元的流程仍是实现高生产率IC实施的关键因素。过去数十年来,单元提取巩固了综合驱动设计流程的基础,为高度自动化的数字电路实施提供了基础,使得小规模团队进行百万门级电路设计成为可能。晶体管结构的变更以及相关的布局依赖效应即将突破设计流程的物理层、单元层和逻辑层之前的清晰接口,这使得设计人员在布局电路时不得不考虑低层特征。但是,通过增强单元级别智能化,可以维持标准单元提取的生产率优势,并且仍然能够获得通过基于finFET的工艺实现的功率、性能和面积(PPA)优势。

伴随finFET而来的是电路结构因其外形变化而导致的根本性变革(图2)。给定工艺的鳍(Fin)结构具有固定的宽度和间距。与平面工艺(可通过任意量增加晶体管宽度来提高整体驱动强度,从而改善大型扇区或高电容总线的性能)相比,finFET的有效宽度只能通过向晶体管添加更多鳍(Fin)结构才能予以改变。鳍(Fin)结构量化不仅提高模拟和自定义电路设计的复杂度,还对数字电路实施产生微妙而重要的影响。

图2:FinFET vs平面型晶体管

总而言之,基于finFET的流程将从尽可能窄的鳍(Fin)结构间距中受益,因为这将提供更好的密度、灵活性和性能。用于创建鳍(Fin)结构的工艺依赖于化学性自动调准技术,该技术可以使间距比金属互联的最精细层(M1和M2)的行间距缩小25%.这些金属层目前使用两个各不相干却又结合为一种合成曝光的的光罩绘制,而非使用自我调准的工艺绘制。这些金属层的最小间距由叠对误差确定,因此采用自我调准的鳍(Fin)结构形成步骤可实现较高间距。设计用于实施大部分数字逻辑(将用于基于finFET的IC)的标准单元时,需要考虑鳍(Fin)结构与M2间距的不匹配性(通常情况下,鳍(Fin)结构平行于M2间距)。

对于基于finFET的工艺,鳍(Fin)结构和金属导线宽间距之间仅存在少数几个能够产生可行标准单元库的有效“齿轮比”,因此需要对其进行设计以便使每个单元都有一个固定数量的布线路径。即便如此,某些组合也会导致金属网格不灵活,使其难以承载关键路径上的单元所需的足够电流。纳米工艺正越来越多地受到电迁移等效应的影响,此类效应使通过强电流的金属线变细直至消失,从而缩短了IC的生命周期。

对于最大的金属布线密度,双掩模的设计规则不仅应用于金属导线宽间距,也应用于其宽度。由此产生的结果是,不能始终绘制更宽的金属导线来承载提供高驱动力的单元所需的强电流。某些鳍(Fin)结构数与金属导线数之比允许在电源布线时更为灵活地使用金属互连工艺。它们支持在需要时使用更宽、更具弹性的电源导轨,与此同时单元的布线路径数能够提供更高的逻辑布线密度以承载功耗。要利用上述结构,需在平时所了解的传统布局布线工具的基础上深入了解标准单元架构,布局布线工具旨在预确定的位置上将标准单位用作为带有一组I/O和电源引脚的黑箱子。

可以使用其对内部标准单元架构的理解并且根据逻辑需求重新映射单元的工具能够额外提供充分利用上述新结构所需的灵活性,而无需彻底重组IC实施流程。相同的理解可以帮助其他设计流程采用最新的设计变更,从而产生工程变更指令(ECO)。

由于设计规则较之以往更具约束性,实施ECO变得更为困难,因为即便是一个小的变更也能导致双模式层的光罩颜色出现问题。整合能够理解本地标准单元环境的工具的流程可以更深层次地进行设计,从而尽可能透明地实施ECO.

深入了解标准单元的内部架构将帮助解决因迁移至基于finFET的纳米工艺而产生的其他问题。由于设计人员试图利用3D晶体管的更高性能并加快时钟速度,他们将遭遇更加严峻的易变性挑战。尽管finFET在某些关键指标方面展示的易变性低于平面型晶体管,但是易变性仍是时序终止的一个主要障碍,并且跨越标准单元和布线层之间的边界以多种方式存在。

传统意义上,此类可变性将整合于限制时钟速度的保护频带中,阻碍获取通过finFET结构实现的性能收益。更好的分析和更正技术可以很大程度上恢复此类性能丢失,从而加快时钟速度并使产品在市场上更具竞争力。

现已证明,14nm和16nm的基于finFET的工艺所采用的双模式技术将导致巨大的路径延迟差异。例如,在调准其中一个用于成像互连模式的光罩时的微小转换可以提高门控电极和电缆之间的耦合电容,从而使路径延迟提高。由于整个光罩的转变将变为一致,因此与该光罩模式相关的晶体管的延迟将得以关联——更多了解每个标准单元行为和内部连接性的高级分析工具也会对其进行考虑。通过考虑上述关联性并采取更正措施,可以消除对耦合电容差异的顾虑并提高目标时钟速度。

互连寄生,尤其是基于finFET的工艺中的金属导线的高抗阻性,也将阻碍时钟树的性能。时钟树使用大量长距离连接以便使IC的时序保持一致。缓冲器插入等传统技术将提高能耗。通过运用基本标准单元的知识,可以执行更为智能的时钟树优化,提供低偏差时序信号,并避免花费功耗预算。

降低器件几何尺寸还可以提高出现因电离辐射而产生的单一事件扰乱的可能性,从而导致结果不正确以及系统崩溃。在电路环境下分析单元结构(有可能使用加强版本替换它们)可以降低在出现阿尔法粒子的情况下行为不恰当的可能性。

采用基于finFET的工艺的这一举措将带来大量流程级的变更,并会对数字设计产生影响。如果不加以解决,将导致较差的IC性能。尽管这些物理效应有可能威胁极度稳定且基于标准单元的流程,但推出在单元层面上解决SoC设计的工具将有助于维持流程的稳定并完全实现基于finFET的工艺所带来的优势。