1.引言

随着电子技术的发展,复杂可编程逻辑器件CPLD(Complex Programmable Logic Device)以其高速、高可靠以及开发便捷、规范、能完成任何数字器件功能的优点[1], 越来越广泛地应用于电子仪器中。

线缆的安装质量的好坏将直接影响电气柜的质量,因此线缆测试是电气柜线缆安装过程中非常重要的环节。线缆快速测试技术是指实时、高效、准确、同时测试多条线缆的连通性能(通断、短路、错接),是目前多数电气传动类企业所希望使用的技术[2]。

本文根据国内外线缆测试技术的发展及生产企业的实际要求,设计了一种新型便携式线缆组快速测试系统。该测试系统采用两块CPLD 用于接口电路,从而实现多组线缆(内有多条导线)同时测试,检测线缆的通断、短路和错接情况,进而达到快速检测线缆连通性能的目的。

2.测试系统工作原理

线缆的连通性是指线缆中任意两根线之间不得短路、断路及错接[3],是其他线缆特性测试的基础。电气柜因型号不同,每组线缆的数量不同,多者可达几十条,少者仅有几条。为了使测试系统的应用具有广泛性,本文将CPLD引入设计中,将被测线缆组接于两块基于CPLD的接口电路之间。用户通过键盘输入待检测线缆组的图号,然后按开始键后CPLD工作,输入的信号通过被测线缆输出到另一CPLD进行数据信息汇总,然后通过SPI(Serial Peripheral Interface)接口模块将数据传递给单片机进行处理,单片机对比接收和发射的数据,从而判断出线缆组中每条线缆的连接状况,并将测试结果通过液晶显示屏显示。测试系统原理框图如图1所示。

3.CPLD 的设计

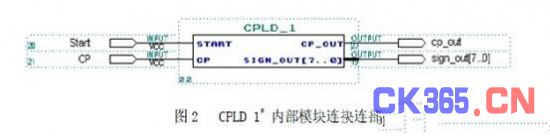

整个测试系统采用两块CPLD(EPM7128),一块作为信号源(CPLD 1#),另一块作为信号采集(CPLD 2#)。CPLD 1#的主要工作是接收单片机发来的‘Start’和‘CP’命令,并以‘CP’为触发信号将‘1’进行移位且并行输出(位数与被测线数相等)。其内部模块连接图如图2 所示[6-7]。

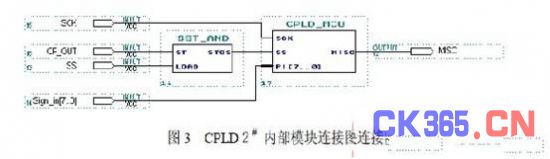

CPLD2# 的主要工作是将由CPLD 1# 输出的信号经过被测线缆进行采集,且将并行位数转换成串行数据传给单片机进行处理,其内部模块连接图如图3 所示,其中包括SST_AND 和CPLD_MCU 两个模块[6-7]。SST_AND 与门电路的主要作用是:只有CPLD 2# 在工作时单片机才能向CPLD 1# 中输出数据,这样保证数据的可靠性和正确性;CPLD_MCU 模块的作用是完成输入数据的并/串转换,将转换好的数据通过SPI 接口传送给单片机。值得注意的是,实际应用时还应在CPLD2#的I/O 口上增加下拉电阻,以避免采集信号时出错。

4.仿真实验

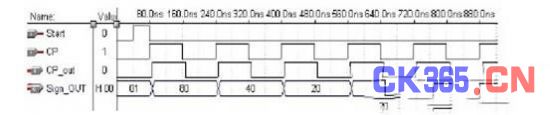

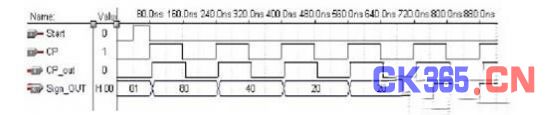

为验证设计的接口电路是否能够实现系统要求,本文对两块CPLD 进行了仿真实验。CPLD1#的仿真波形如图4 所示。

图4 CPLD1# 仿真波形

由图4 可知,当CPLD1#接收到‘Start’命令后,在‘CP’触发信号的作用下,Sign_out 端口依次输出(00001000)B、(00010000)B、(00100000)B 等信号,实现了将‘1’进行移位且并行输出。

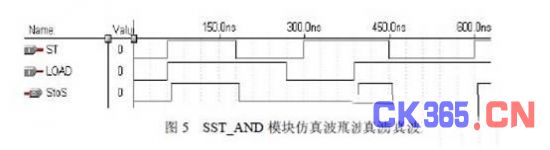

SST_AND 模块的仿真波形如图5 所示,CPLD_MCU 的仿真波形如图6 所示。

在图5 中,SS 端的信号来自单片机,当SS 端的信号与CPLD1#的CP_out 端信号皆为高电平时,CPLD2#才可开始采集信号。由图6 可知,由CPLD1#输出的8 位并行数据(10101101)B 经Sign_in 端口进入CPLD2# 的 CPLD_MCU 模块进行转换,MISO 端输出为串行数据。

通过图 4-图6 的仿真结果可知,设计的CPLD 接口电路能够实现多条线缆的同时测量。本文设计的CPLD 接口电路最多能同时测量64 条线缆的连通性能(受CPLD芯片I/O 引脚数量的限制),若要同时测试更多线缆,只需更换CPLD 芯片即可。

5.总结

本文作者创新点:利用CPLD 器件I/O 接口多的优点,创新地将CPLD 引入到线缆测试技术中,实现了多条线缆连通性的同时测量。仿真实验证明设计思路正确,方案可行,为高效、准确地实现电气柜线缆组的测试提供了新的、有效的途径。