CMOS问世比TTL较晚,但发展较快,大有后来者居上、赶超并取代之势。

1、组成结构

CMOS电路是互补型金属氧化物半导体电路(Complementary Metal-Oxide-Semiconductor)的英文字头缩写,它由绝缘场效应晶体管组成,由于只有一种载流子,因而是一种单极型晶体管集成电路,其基本结构是一个N沟道MOS管和一个P沟道MOS管,如图1所示。

由于两管栅极工作电压极性相反,故将两管栅极相连作为输入端,两个漏极相连作为输出端,如图1(a)所示,则两管正好互为负载,处于互补工作状态。

·

当输入低电平(Vi=Vss)时,PMOS管导通,NMOS管截止,输出高电平,如图1(b)所示。 ·

当输入高电平(Vi=VDD)时,PMOS管截止,NMOS管导通,输出为低电平,如图1(c)所示。

两管如单刀双掷开关一样交替工作,构成反相器。

2、制造工艺

CMOS电路中的主要组成是金属、氧化物、半导体管,做在同一基片上,其间自然是隔离的,无需专门的隔离措施。

图2为CMOS反相器的芯片结构示意图。

在制造时,首先在N型硅衬底上扩散P型区,这个P型区通常叫做P阱,也就是N-MOS管的衬底;在P阱内再用扩散法制作两个N型区,以形成N-MOS管(N沟道MOS管)。而P-MOS管则可直接做在N型硅衬底上。

由上述可见,CMOS电路比双极型电路制造工艺简单、工序少,由于节省了隔离槽占用的面积,还可大大提高电路集成度。当然,若与单沟道MOS电路相比,工艺上要稍复杂些,例如它要多用两块光刻板,还需要P阱保护环,因而芯片利用率也要低些。

3、电路特点

1) 功耗

表1列出了各种MOS电路的四个主要参数。

CMOS电路采用互补结构,工作时总是一个MOS管处于导通、另一个MOS管处于截止状态,因而电路功耗理论上为零。

实际上,由于存在硅表面和PN结的泄露电流,量值约数百毫微安,因而尚有微瓦量级的静态功耗,但相比于TTL电路则低多了。

功耗低,这是CMOS电路的一个突出优点。

图3为两种电路的动态功耗电流曲线。

由图3曲线可见,TTL比CMOS电路功耗大,但随频率提高其功耗所增无几,而CMOS电路的功耗却随频率提高急剧增大,因而CMOS电路宜用于较低频率。

2) 抗干扰能力

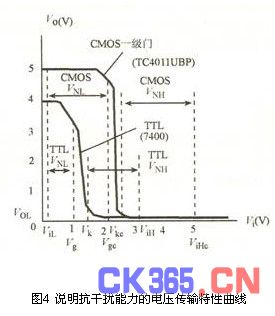

抗干扰能力又称噪声容限,它表示电路保持稳定工作所能抗拒外来干扰和本身噪声的能力,可用图4电压传输特性来说明。

在图4曲线中,ViL为本级门最大输入低电平,Vg为关门电平,Vk为开门电平,ViH为最低输入高电平。显然,要保持输出高电平,干扰电压不应超过:

图4是在电源电压为5V时的典型曲线,由图可知,CMOS曲线比TTL变化陡,其Vgc与Vkc值接近约为2V,且输入、输出电压范围也比TTL大,因而其抗干扰能力较强。

3) 工作速度

电路的工作速度一般用平均传输延迟时间tpd表示。它说明输出信号比输入信号在时间上落后了多少,也就是信号通过一级门所花费的时间。当然,希望tpd值越小越好。

表1中所列tpd值是在环境温度25ºC,供电电压5V同一条件下,对与非门电路的测试值。由表可见,CMOS电路的工作速度比PMOS和NMOS电路要高得多,但比TTL电路要低约一个数量级。

前已述及,工作速度的提高在功耗上是要付出代价的,这也就是CMOS电路不宜用于高速控制系统的主要原因。

4) 扇出系数

在实际应用中,要完成复杂的逻辑运算,一个门电路总是要驱动若干个其他门电路的,因而后级门就成前级门的负载。一个门能驱动的门的个数是有限制的,通常用能驱动同类门的最大个数来表示一个门的负载能力,这个数值叫做扇出系数No。

影响No的因素主要有二:

1) 电路输出管允许的倒灌电流;

2) 门电路本身的短路输入电流。

由电路结构可知,CMOS电路的输入端是栅氧化膜,其阻值高达数百兆欧。实际上由于在输入端设置的保护电阻和保护二极管PN结的漏电,使输入阻抗下降至数十兆欧,尽管如此,它比TTL电路要高得多。

由于CMOS电路的输入阻抗极高,在级联时几乎不取负载电流,因而其扇出系数要比TTL电路约高出一倍。