电路功能与优势

图1所示电路是14位、125 MSPS四通道ADC系统的简化图,该电路使用后端数字求和将信噪比(SNR)从单通道ADC的 74 dBFS提升到四通道ADC的78.5 dBFS。这项技术特别适合要求高SNR(如超声和雷达)的应用,并且利用了现代高性能、低功耗、四通道流水线式ADC。

该电路使用了非相关噪声源在方和根(rss)基础上相加,而信号电压在线性基础上相加的基本原理。

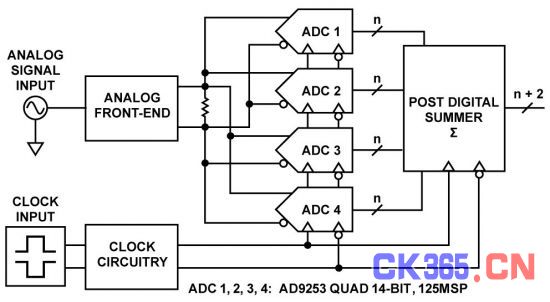

图1. 四个并联ADC求和得到更高SNR的基本框图

电路描述

每个ADC的输入由信号项(VS)和噪声项(VN)组成。将四个噪声电压源求和可得到总电压 VT, 它是四个信号电压加上四个噪声电压方和根的线性和,例如:

由于VS1 = VS2 = VS3 = VS4,信号可有效地乘以4,而转换器噪声——具有等效rms值——仅乘以2,因此信噪比以系数2增加,即6.02 dB。所以,6.02 dB的SNR增量是将四个类似信号求和所引起的一个额外的有效分辨率位的结果。由于 SNR(dB) = 6.02N + 1.76 dB,其中N为位数,从而

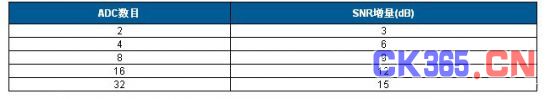

表1显示将多个ADC输出求和得到的SNR理论值。为方便起见,显然应选择将四个ADC求和。某些关键情况下可能需要更多的ADC求和,但具体取决于其他的系统规格(包括成本)和可用的电路板空间。

表1. 增加SNR与ADC数目的关系ADC数目SNR增量(dB)

14位ADC的理想SNR是(6.02 × 14) + 1.76 = 86.04 dB AD9253 数据手册指定的典型SNR为74 dB,但其产生的ENOB为12位。

图1所示电路集成无源接收器前端,由四个模拟输入通道组成,采用器件为14位、125 MSPS四通道模数转换器 AD9253 。

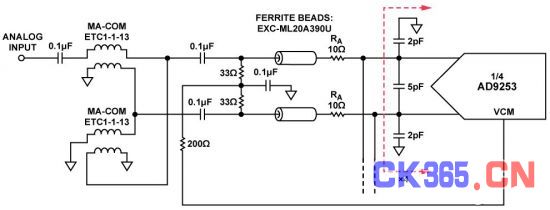

该电路接受单端输入,并通过双平衡配置中两个阻抗比为 1:1的宽带宽(3GHz) M/A-COM ETC1-1-13巴伦将输入转换为差分信号,如图2所示。

图2. 输入模拟求和网络

所有四个ADC输入均在巴伦配置的次级侧相连。电路中无增益,每个模拟输入对都有简单滤波功能,减少可能反馈至邻近ADC通道的残余反冲信号。

通过ADC的全差分架构提供良好的高频共模抑制性能,因此求和时非相关噪声源最小,产生78.5 dBFS SNR和85dBc SFDR性能(第一奈奎斯特频带内,以125MSPS采样时0MHz 至62.5MHz)。整体电路带宽为65 MHz,通带平坦度为1dB。

为了获得最佳性能,采用双平衡巴伦法在频率范围内达到最佳的偶阶杂散性能。由于四个ADC的输入相连,维持平衡可能有一定难度,哪怕频率低于100 MHz。

使用66Ω差分端接电阻端接巴伦配置的次级侧。选择66 Ω有助于减少四个转换器输入阻抗并联组合的损耗,同时最大程度降低变压器次级侧对初级侧的损耗,获得从初级侧看来大约50Ω的总阻抗。

此设计中采用了铁氧体磁珠,有助于降低电路板布局以及四个未缓冲并联ADC通道引起的寄生容性负载的影响。磁珠可减少来自每个ADC输入通道的反冲,从而保持了整体带宽。

10Ω串联电阻具有双重作用。首先,它们驱动ADC输入滤波器(2pF共模和5pF差分);其次,它们起到减少来自每个 ADC反冲的作用。有关反冲充电和未缓冲ADC架构的更多信息,请参见应用笔记AN-742。

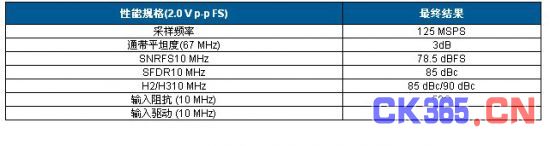

表2总结了系统的测量性能,其中−3 dB带宽为67 MHz。网络的总插入损耗约为3dB,因此需要+13dBm的输入驱动能力,以便为ADC的输入提供满量程2Vp-p差分信号。

表2. 电路的测定性能 性能规格(2.0 V p-p FS)最终结

系统性能

14位、125 MSPS、四通道ADC AD9253 与16位、125 MSPS ADC AD9653引脚兼容。图3显示AD9253和 AD9653四通道求和配置的带宽测量对比。

图3. AD9253和AD9653四通道求和配置的频率响应

针对单通道和四通道版本的 AD9253 和 AD9653 测量SNR,结果显示在图4中。

图4. AD9253、AD9653单通道和四通道求和配置的SNR性能与频率的关系

请注意,使用四通道求和技术,可增加14位ADC AD9253 在 10 MHz时的SNR,增加量约为5dB。16位ADC AD9653 的SNR增加量大致相同。

另一方面,单个14位ADC AD9253和单个16位ADC AD9653相差大约3 dB。

SFDR数据用于AD9253 和 AD9653, 的四通道求和配置,如图5所示。

图5. AD9253和AD9653四通道求和配置的SFDR性能与频率的关系

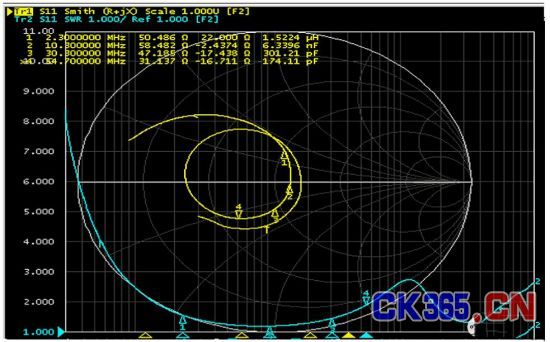

图1和图2中所示电路的输入阻抗使用一个在1 GHz频段内校准至50Ω的网络分析仪测量,如图6所示。可以看出最终网络在所需频段内(第一奈奎斯特区,直流至62.5 MHz)的VSWR为1.2或更低。

图6. 完整前端四通道求和的输入阻抗

前端接口设计程序

知道并理解设计前端时的关键参数,包括:

输入阻抗/VSWR(电压驻波比)是一个无量纲参数,反映目标带宽内有多少功率被反射到负载中。网络的输入阻抗是特定的负载值,通常为50Ω。

通带平坦度通常指额定带宽内容许的波动纹波量。

带宽仅仅是系统要使用的频率范围。

最小信噪比(SNR)和无杂散动态范围(SFDR)

输入驱动电平与带宽、输入阻抗和VSWR特性有关,可设置转换器满量程输入信号所需的增益和幅度。它高度依赖所选的前端元件,如变压器、放大器或抗混叠滤波器,并且可能是最难以达到的参数之一。

ADC与滤波器的负载间必须确定正确数量的串联电阻。这是为了防止通带内的不良信号尖峰,并尽量减少单个 ADC输入的反冲。在大部分情况下,必须凭经验确定正确值。

ADC的输入阻抗可能需要经过外部并联电阻分流,才会降低数值。

应使用正确串联电阻将ADC与滤波器隔离开。此串联电阻也会减少尖峰信号,且通常凭经验确定。

电路优化技术和权衡

本接口电路内的参数具有高互动性;因此优化电路的所有关键规格(带宽、带宽平坦度、SNR、SFDR和增益)几乎不可能。

在图2中,通带峰化可以随着串联电阻RA的值提高而降低。但是,此电阻的值越高,信号衰减就越大,输入网络必须以更大的信号驱动,以填充所有ADC并联组合的满量程输入范围。

上述因素的权衡可能有些困难。本设计中,每个参数权重相等;因此所选值代表了所有设计特征的接口性能。某些设计中,根据系统要求,可能会选择不同的值,以便优化 SFDR、SNR或输入驱动电平。

本设计的SNR性能取决于以下几个因素:ADC架构的本质、通过内部采样和保持机制设置的 AD9253 3内部前端缓冲器偏置电流,以及设计的带宽要求。本例中使用了整个第一奈奎斯特区。

该特定设计中可以权衡的另一因素是ADC满量程设置。对于采用本设计获得的数据,满量程ADC差分输入电压设置为2 V p-p,它可以优化SFDR。将满量程输入范围改为低于 2.0 V p-p的最大满量程范围会降低SNR性能。

无源组件和PCB寄生效应考虑

该电路或任何高速电路的性能都高度依赖于适当的PCB布局,包括但不限于电源旁路、受控阻抗线路(如需要)、元件布局、信号布线以及电源层和接地层。高速ADC和放大器PCB布局的详情请参见指南 MT-031和 MT-101。

对于滤波器内的无源元件,使用低寄生表面贴装电容、电感和电阻。所选电感来自Coilcra0603CS系列。滤波器使用的表贴电容为5%、C0G、0402型,以确保稳定性和精度。

系统的完整文档请参见CN-0249设计支持包。

常见变化

对于需要相同带宽、更低功耗和性能的应用,可使用12 位、125 MSPS四通道ADC AD9633。对于需要相同带宽、略高功耗和更高性能的应用,可使用16位、125 MSPS四通道 ADC AD9653。这些器件与之前列举的其他器件引脚兼容。