一、引 言

本文所讨论的超高速数字信号处理,是指数百兆带宽信号的数字采集、处理技术超高速数字信号处理技术具有很多独特的问题,必须进行仔细的分析和研究.

本文的目的,就是综述超高速雷达数字信号处理技术的应用背景、研究内容、关键技术及解决方案,并介绍作者已经实现的一些超高速雷达数字信号处理系统.

二、超高速数字信号处理在雷达中的应用

1.距离高分辨率雷达数字信号处理

距离高分辨率雷达具有多种优点[1].对于最为常用的线性调频脉冲(CHIRP)信号,为实现0.1~1m的距离分辨率,要求信号带宽可以达到150~1500MHz[2],因此是超高速数字信号处理技术的主要应用之一.

2.合成孔径雷达数字信号处理

合成孔径雷达是当前雷达侦察的主要方式之一[3],其分辨率已经从早期的10m量级发展到目前的1m~0.1m量级[4],因此同样需要进行超高速数字信号采集与处理.

3.电子对抗与反对抗

在电子对抗和反对抗领域,数字射频存储器技术是近年研究的热点[5].数字射频存储器的主要指标之一是瞬时带宽,其中3-bit量化的数字射频存储器带宽已经可以达到17GHz,8-bit量化的数字射频存储器带宽也可以达到220MHz[6].因此,数字射频存储器的基础也是超高速数字信号采集与处理技术.

4.雷达数字接收机

当前雷达系统研究中已经提出了雷达数字接收机的概念,并在频率较低的米波雷达中首先获得了应用[7].雷达数字接收机的关键技术是对微波信号的采集和处理[7],因此同样需要采用超高速数字信号处理技术.

5.多功能雷达信号产生与处理

雷达系统具有多种发射波形可以匹配不同的应用环境、通过多波形的组合使用取得最优的效果[8].直接数字合成(DDS)技术是数字波形形成的主要方法之一.当前DDS器件的水平已经可以达到400MHz[9],因此也是超高速数字信号处理技术的应用背景.

6.雷达信号/干扰模拟器

在雷达系统的研制中,为了在天线和微波前端不具备的条件下对雷达数字信号处理机进行调试,需要雷达视频信号/干扰模拟器[10].对于距离高分辨率雷达、合成孔径雷达,雷达信号/干扰模拟器也要能够模拟宽带视频信号,因此也是超高速数字信号处理技术的应用领域之一.

三、超高速数字信号处理的主要内容与特殊问题

1.超高速数字信号处理的主要研究内容

超高速数字信号处理主要包括以下研究内容[11]:

(1)超高速数据采集 超高速数据采集是整个超高速数字信号处理的最前端,包括超高速AD变换和超高速数据存储.其中超高速AD变换的特殊问题是其中的超高速模拟电路,即AD变换的精度.它是整个超高速数字信号处理性能的基础.

(2)高速实时数字信号处理 高速实时数字信号处理要完成对采集的超高速数据进行信号检测、截获、跟踪等处理,并具备不断修改、完善的潜力;因此其主要特点是实时性、多功能、可编程,故多采用高速实时数字信号处理芯片(DSP芯片)构成.当前先进DSP芯片的主要代表是TMS320C8x、TMS320C6x和ADSP2106x芯片等等.

(3)超高速信号生成与信号模拟 这里的超高速信号生成指的是通过直接数字合成(DDS)方法产生各种雷达信号,因此其中核心的问题是超高速DA转换.这里的超高速信号模拟指的是通过数字仿真的方法模拟宽带雷达视频回波信号,因此核心的问题也是超高速DA转换.

2.超高速数字信号处理的特殊问题

超高速数字信号处理的特殊问题主要表现在以下几个方面[11,12]:

(1)元器件选型 芯片选型的问题主要在于两个方面:一方面,传统的TTL芯片不能满足超高速数字信号处理的速度要求,必须采用更高速的芯片类型.另一方面,AD变换器、DSP芯片、专用芯片(如FFT、数字相关)、及DA变换器等芯片的选型应与系统的要求进行最佳匹配.

(2)体系结构 系统的体系结构必须在信号带宽、数据存储量、数字信号处理速度等多项要求之间进行最优的折中.由于系统速度要求很可能超过单片采集或处理芯片的速度极限,因此必须考虑采用多路并行的体系结构.

(3)数字电路的硬件实现 在硬件电路的实现中,由于信号之间的连线存在电阻、电容和电感,因此会造成信号的延迟、反射、串扰和噪声.这些现象在中低速系统中通常可以忽略,但是在超高速系统中则会变得非常严重.例如,印制板上的线每英尺会造成约2ns的延迟量,这一延迟在中低速系统中可以不考虑,而在超高速系统中它已等同甚至超过一级门延迟.所以,超高速数据采集系统中的信号连线必须进行特殊的处理,才能保证系统的正常工作.

(4)模拟电路的抗干扰 在超高速数据采集、超高速信号生成/信号模拟等应用场合,除了数字电路之外,还有运算放大器、A/D变换器、D/A变换器等模拟器件.这些模拟器件很容易受到各种干扰,必须采取各种抗干扰措施来保证它们的精度.

(5)系统功耗与散热 超高速系统的电流一般都远大于中、低速系统,因为超高速系统实际上是以大电流来换取高速度的.系统功耗引起的温升会使芯片的性能下降,严重时甚至会造成芯片的损坏.因此必须在系统设计时进行热性能分析,并仔细研究系统散热的方法.

(6)超高速数字信号处理的软件算法 典型的雷达数字信号处理算法可分为底层算法和高层算法.底层算法主要是提高信噪比、抑制杂波等算法,包括脉冲压缩、滤波、恒虚警率处理、信号检测等.高层算法主要是雷达成像、目标识别等算法.此外,在电子对抗、信号生成、信号模拟等方面,也有其特殊的算法需要研究.

超高速信号处理算法中一个比较独特的问题是需要研究信号处理算法的并行性、算法与硬件结构的最佳匹配问题.这是因为信号采集速度极高,要求信号的快速处理.在单片信号处理芯片性能不足的情况下,必须研究并行处理的处理机结构和与之相应的算法.

四、超高速数字信号处理关键技术的解决方案

1.元器件的选型[13]

对于超高速数字信号处理系统,传统的TTL芯片已无法工作.目前常用的超高速标准芯片系列是ECL芯片;其不同系列的最高工作频率可以达到250M、500M、甚至1600MHz(表1).对于更高速的系统;则需要采用砷化镓器件构成.

表1 常用芯片的最高触发器翻转频率(单位:MHz)

TTLTTLTTLTTLCMOSCMOSECLECLECLECL

74LS74ALS74S74AS74HCT74ACT10K10KH100K100E

335095125501251502503751600

2.数字电路的实现[14]

在数字电路的实现中,主要需要解决信号的延迟、反射、串扰、噪声问题.解决这些问题的方法,就是采用微波传输线作为信号之间的连线.微波传输线在端接电阻匹配的条件下可以消除反射,并精确控制信号的延迟.由于ECL芯片本身具有驱动50Ω端接传输线的能力,这就为微波传输线的实现奠定了基础.

3.模拟电路抗干扰[15]

模拟电路的干扰源主要包括空间电磁辐射的干扰、信号线之间的串扰、地线和电源线的共模干扰等因素.可以采用屏蔽、大面积接地、元器件的合理布局、电源滤波等多种手段解决这一问题.例如,可以采用铁氧体磁芯加电容滤波的方法来取得最好的滤波效果,并采用星形接地的方法来减小地线上的共模干扰.

4.体系结构的选择

体系结构的设计可以分为多个层次:最顶层的设计是整个数字信号处理系统的体系结构;进一步细化的层次是AD、存储器、DSP、DA等模块的体系结构.超高速系统体系结构最重要的特点就是各种层次上的并行性;而具体系统的体系结构设计则要根据不同的应用条件而定.

5.系统功耗与散热[11]

由于超高速系统的功耗很大,因此在系统设计时就必须把热设计作为必需的组成部分;在设计阶段就要仔细分析各个芯片的功耗、热阻、温度范围及推荐的散热方法.对于必须进行强制制冷的系统,可以在风冷、液冷等方案之间进行选择;一般来说,只要选择合适的风冷方法就可以使系统正常工作.

6.采用先进的分析手段[16]

电子设计自动化(EDA)技术可以对超高速系统的设计提供极大的帮助.先进的EDA工具可以分析PCB上传输线的延迟、反射和串扰,并对系统功耗和温度进行分析;采用先进的EDA工具还可以在严格定义的布线条件下完成系统的自动布线,因此可

五、超高速数据采集系统的实现

对于1m距离分辨率的雷达系统,其采样速率可以达到250MS/s,其主要问题是:

1.体系结构的选择

(1)AD变换的体系结构[17] 在AD转换模块中,可以采用单片AD的结构,也可以采用多片AD并行的结构;而多片AD并行又包括时间并行和幅度并行两种方式.多片AD并行可以降低对每一AD芯片的性能要求,但增加了设备量和控制的复杂性.在超高速应用的场合,一般采用的是单片AD变换的结构.

(2)数据存储的体系结构[18] 由于超高速数据采集系统的速度很快,因此存储模块的设计一般都采用分路数据输出的体系结构;这种结构将AD的输出数据分成多路较低速数据输出,可以降低对存储器读写速度的要求.

2.元器件的选型与信号连线的处理

根据表1,对于250MS/s的数据采集系统,传统的TTL芯片已无法工作.目前常用的超高速标准芯片系列是ECL芯片;对于250MS/s的采样速率,ECL10KH系列可以满足要求.

根据前面的分析,超高速系统的信号连线必须采用微波传输线作为信号之间的连线,并要进行正确的端接.这样就可以消除反射,并精确控制信号的延迟.

3.模拟电路的抗干扰

系统抗干扰的方法首先是屏蔽,包括电路整体的屏蔽以及系统模拟部分和数字部分之间的屏蔽.但是由于超高速系统一般是高功耗的,因此还必须兼顾散热问题.

数据采集系统中数字电路对模拟电路的干扰是主要误差源之一.消除这一干扰可以通过器件的隔离、电源滤波、星形接地以及元器件的合理布置来解决.在超高速系统的实现中,大面积地是一个最基本、也最重要的因素之一,一方面它可以减小干扰,另一方面它也是微带传输线的一个组成部分.

4.系统的实现与性能测试

(1)系统的实现 系统中采用了单片超高速AD芯片加全局存储器的体系结构,并采用单片机构成系统与IBM-PC计算机的接口,使数据采集的结果可以在计算机中显示并加以处理(图1).其中,为降低对存储器速度的要求,采用了分路数据输出的方式,使存储器的速度降低为AD变换速度的一半.存储器的周边器件采用ECL芯片.信号之间的连线采用微带或带状传输线,并端接了合适的端接电阻.

图1 超高速数据采集系统的体系结构

(2)系统性能测试 数据采集系统的性能测试主要包括静态测试和动态测试,其中动态测试更能够全面地反应系统的性能.在动态测试中最为关心的指标是动态有效位(ENOB).本系统在250MS/s采样速率、125MHz输入信号时测试了系统的动态有效位,可以证明,系统的动态有效位在7-bit以上.

六、高速数字脉冲压缩系统的实现

1.脉冲压缩的基本原理[8]

脉冲压缩算法的基础在于匹配滤波的理论.假设发射信号为S(t),其频谱为S(ω);并设匹配滤波器的冲击响应为h(t),传递函数为H(ω),则脉冲压缩后的信号输出为:

Y(ω)=H(ω).S(ω) (1)

y(t)=h(t)

s(t) (2)

这里,只要匹配滤波器的冲击响应/传递函数与发射信号满足匹配滤波关系,就可以获得脉冲压缩的输出结果.

2.脉冲压缩的主要实现方法

(1)时域法实现脉冲压缩 时域法实现脉冲压缩的基础是式(2):由于匹配滤波在时域等效于相关接收,因此,时域法实质上就是数字相关的方法.图2显示了相关数字脉压的基本结构.其中,采集的原始信号与预先存储的参考码送入相关器,相关器的输出就是脉压后的数字结果;可以采用DA变换将其变为模拟信号显示.

图2 时域法实现数字脉压

(2)频域法实现数字脉压 频域法实现数字脉压的基础是式(1),其基本结构示于图3.这里,采集的原始信号首先通过FFT变换到频域,与预先存储的参考码相乘后,再通过逆FFT变换回时域,就构成脉压后的数字结果;同样可以采用DA变换将其变为模拟信号显示.由于FFT算法相当于快速卷积,因此频域法的运算速度一般要快于时域法,尤其在压缩比较大的情况下.

图3 频域法实现数字脉压

3.一种高速实时多功能数字脉冲压缩系统的实现

采用频域法实现了一个高速实时多功能数字脉冲压缩系统;系统的体系结构就采用图3的方式.这里,系统实时性的关键问题是FFT芯片的速度;我们选择了可在98us时间内完成1024点FFT的高速专用FFT芯片.系统中存储参考码的EPROM可以存放不同的匹配滤波器参数,只要变换EPROM的地址,就可以实现对不同信号形式的脉冲压缩.因此,这是一种高速、实时、多功能的数字脉冲压缩系统.

七、超高速雷达信号发生器/回波模拟器的实现

1.直接数字合成法实现超高速信号发生器

DDS的基本原理如图4所示[20],其核心内容是超高速D/A变换器和一个正弦查找表.这里,正弦查找表存储了一个完整的正弦波在不同相位上的幅度值;因此,只要改变正弦查找表的寻址方式,就可以获得不同类型的数字信号;再经过DA变换器和低通滤波器,就是所需要的模拟信号.

图4 DDS技术的原理框图

2.超高速雷达回波模拟器的实现

(1)雷达回波模拟的基本原理[10] 雷达回波模拟器的实质是“分立DDS”的方法,即把DDS的数据存储器(即DDS中的正弦查找表)和DA变换器分离开,并采用随机存储器RAM代替DDS中的ROM.这样,在分立的随机存储器内可以存储各种复杂的雷达回波数据,而且可以实时修改,这样就可以实现各种目标回波和干扰背景的模拟.

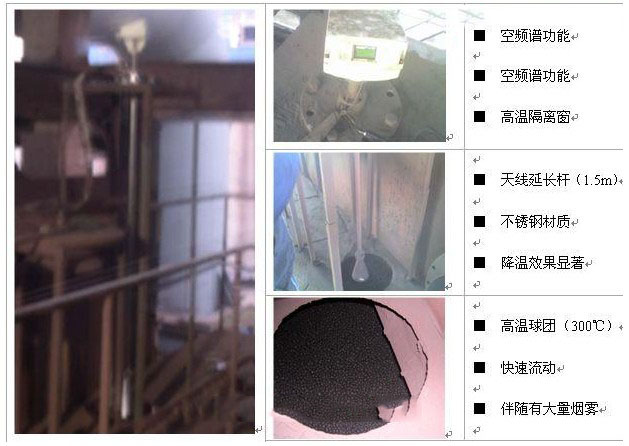

(2)雷达回波模拟的主要模块 雷达回波模拟器主要包括数据生成、数据调度、DA转换三个模块;如果要求模拟产生中频或射频回波,则还要包括载频调制模块(图5).这里,数据生成模块产生雷达目标、噪声、杂波、干扰等互相叠加的复杂回波数据;数据调度模块主要用于生成实时回波数据;D/A转换和低通滤波模块用于生成所需要的模拟视频回波信号.

图5 雷达回波模拟器的原理框图

(3)超高速雷达回波模拟器的实现 采用图6介绍的方法实现了一个超高速雷达回波模拟器.模拟器的时钟频率为250MHz,因此模拟器的输出频率最高可达125MHz(图6).

图6 超高速雷达回波模拟器的实现框图

3.采用超高速雷达回波模拟器产生多种雷达发射信号

以上介绍的超高速雷达回波模拟器不仅可以用作回波模拟,而且可以用作信号生成.这里,如果在图6的多路全局存储器中存放正弦查找表,则图6实际上就是一个DDS系统.

采用回波模拟器产生信号与DDS芯片的主要差别是:一、DDS在同一时间只能产生一种信号,而回波模拟器可以在同一时间产生多种不同信号的叠加;二、DDS可以产生具有任意相位分辨率的连续信号,而回波模拟器由于循环寻址比较困难,因此只能产生一些特定频点的信号,其产生信号的频点数受到全局存储器容量的限制.