引言

当前,越来越多的通信系统工作在很宽的频带上,对于保密和抗干扰有很高要求的某些无线通信更是如此,随着信号处理器件的处理速度越来越快,数据采样的速率也变得越来越高,在某些电子信息领域,要求处理的频带要尽可能的宽、动态范围要尽可能的大,以便得到更宽的频率搜索范围,获取更多的信息量。因此,通信系统对信号处理前端的A/D采样电路提出了更高的要求,即希望A/D转换速度快而采样精度高,以便满足系统处理的要求。

可编程门阵列FPGA的出现已经显著改变了数字系统的设计方式。应用可编程门阵列FPGA,可使数字系统设计具有高度的灵活性,因此FPGA的应用越来越广泛,而新一代FPGA--Virtex Ⅱ-PRO的出现使FPGA的功能更加强大,但随之而来的是要求提高数据的传输速率,过去人们总是关心如何提高处理器运行速度,而现在关心的是怎样才能更快地将数据从一个芯片传输到另一个芯

片。可见,高速数据采集系统的输入输出接口设计就显得尤为重要。

1 高速采集系统介绍

数据采集系统原理框图如图1所示,输入的中频信号经A/D采样电路采样后,转换成LVDS信号送入FPGA中,或通过FPGA的端口RocketIO从高速接口输出,或通过FPGA的端口LVDS循环存储于高速缓存中,再由低速接口输出。其中,FPGA主要完成对外接口管理、高速缓存的控制和管理。时钟控制电路对A/D数据转换器和可编程门阵列FPGA起同步和均衡作用。

2 输入输出接口研究

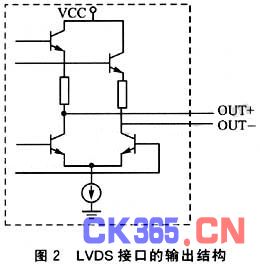

Virtex Ⅱ-PRO系列是在Virtex Ⅱ系列FPGA的基础上,嵌入了高速I/O接口和IBM PowerPC处理器,它能实现超高带宽的系统芯片设计,支持LVDS,LVPECL等多种差分接口,适应性很强。其中高速串行(MGT)技术采用了RocketIO技术,在可编程逻辑器件中内嵌了速率为3.125Gb/s的多端串行通信接口,该技术包括千Mb以太网、10千以太网、3GIO、SerialATA、Infiniband和Fibre Channel,为高性能接口提供了完成的解决方案。LVDS(Low Voltage Differential Signaling)信号标准是一种小振幅差分信号技术,如图2所示,它使用非常低的幅度信号(100-450mV),通过一对平行的PCB走线或平衡电缆传输数据。在两条平行的差分信号线上流经的电流方向相反,噪声信号同时耦合到两条线上,而接收端只关心两信号的差值,于是噪声被抵消。由于两条信号线周围的电磁场也互相抵消,故差分信号传输比单线信号传输电磁辐射小很多,从而提高了传输效率并降低了功耗。

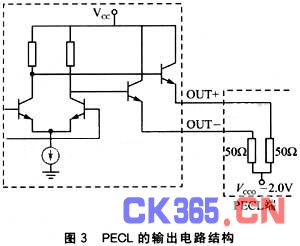

在高速数据采集系统中,使用了最新的A/D芯片MAX104A。该芯片是Maxim公司的最新产品,采样频率可以达到1GHz,采样精度为8位。芯片输出是PECL(Positive Emitter-Coupled Logic)电平输出。PECL信号的摆幅相对ECL要小,适合于高速数据的串行或并行连接。PECL的输出电路结构如图3所示。该电路包含一个差分对管和一对射随器。输出射随器工作在正电压范围内,无信号时电流始终存在,这样有利于提高开关速度,标准的输出负载接50Ω电阻至VCCO-2V的电平上,如图3所示,在这种负载条件下,OUT+与OUT-的静态电平典型值为UCCO-1.3V,OUT+与OUT-输出电流为14mA。PECL结构的输出阻抗很低,典型值为4-5Ω,这表明它有很强的驱动能力。但当负载与PECL的输出端之间有一段传输线时,低阻抗造成的失配将导致信号时域波形的振铃现象。