摘要:介绍了一种基于FPGA的超高速数据采集与处理系统,给出了系统实现的方案,并详细阐述了各硬件电路的具体构成。对系统软件功能做了简要介绍,并利用嵌入式逻辑分析仪对该超高速数据采集系统进行了测试,验证了采样结果的正确性。该超高速数据采集与处理系统通用性和可扩展性较强,适合工程应用。

0 引言

在电子信息领域中,通常要求处理的频带要尽可能的宽、动态范围要尽可能的大,以便 得到更宽的频率搜索范围,获取更多的信息量,这就要求A/D 转换速度快而采样精度高,以 便满足系统处理的要求[1]。随着电子元器件的不断发展,ADC 的采样速率越来越高,很多公 司都推出了采样率可达GHz 以上的产品。例如MAXIM 公司的MAX108 芯片,采样精度为 8bit,采样率可达1.5Gsps;国家半导体公司(National Semiconductor)的ADC08D1500 芯片, 单片集成双通道,采样精度为8bit,单通道采样率可达1.5Gsps,另外新品ADC08B3000,单 通道芯片,采样精度为8bit,单通道采样率可达3Gsps;Atmel 公司推出的AT84AS004 芯片, 采样精度为10bit,采样率可达2 Gsps,另外商用10 位ADC AT84AS008GL,时钟频率达 2.2Gsps [2]。

本文介绍了一种基于 FPGA 的超高速数据采集与处理系统,该系统采用了国家半导体公 司(National Semiconductor)的高速采样器件ADC08D1000 芯片与ALTERA 公司的Stratix 系 列FPGA 芯片,可实现采样速率1GHz 的双通道数据采集和采样速率为2GHz 的单通道数据采 集。另外,考虑到该数据采集系统的后续数据处理问题,采用了TI 公司的TMS320C6000 系 列DSP 芯片完成后端数据的处理。

1 系统硬件设计

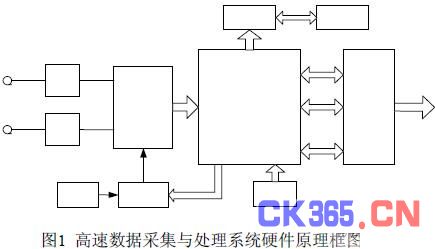

本文设计的基于FPGA的高速数据采集与处理系统硬件原理框图如图1所示,该数据采集 系统为双通道数据采集系统,单片ADC08D1000集成了双通道模数转换功能,采样速率为 1GHz。如果该系统只需要完成一路信号的数据采集,那么可以选择ADC08D1000工作于交叉 采样模式,此时,只需要将信号接于信号输入1端,信号输入2端悬空,这样即可实现采样速率为2GHz信号的数据采集。采样后的数字信号送入FPGA进行预处理,预处理后的数字信号送 入DSP做相应的后续处理。另外,可通过USB接口芯片将所需数据传给PC机,完成数据的存 储、处理与显示等。

1.1 PLL 时钟电路

该高速数据采集系统工作所需的时钟频率为1GHz,为了能提供一个稳定的时钟,该系统 时钟源采用了ADI公司新推出锁相环频率合成器ADF4360-7。该芯片是个集成的整数N合成器 和压控振荡器(VCO)。它的中心频率由外置电感决定,频率范围从350MHz到1800MHz。另 外还有一个二分频可选择,这样使用者可以得到175MHz~900MHz的RF输出。该芯片采用简单 的3线控制来完成所有寄存器的控制与使用。

该芯片输出频率计算公式如下:

其中 REFIN f 为输入参考频率;P为分频模数;A、B、R分别为三个寄存器的输入值。ADF4360 -7芯片提供8 /9或16/17两种计数模式,一般情况下,当输出频率较高的时候选用16 /17计数器, 输出频率较低的选用8/9 计数器。根据上面的公式,为了系统输出1GHz 的频率, 当 f REFIN = 16MHz 时,通过计算可得出:当R = 16,P = 16,B = 62,A = 8时,满足公式 的0 f 输出为1GHz。另外为了能正确配置该芯片,要求三个寄存器的配置顺序依次为:R寄存 器、C寄存器和N寄存器。且根据电容N C 值选取的不同,C寄存器和N寄存器之间的时间间隔 必须满足一定的要求。由于该系统中C N = 10 uF,因此C寄存器和N寄存器之间的时间间隔T 必须满足T ≥ 10ms。

1.2 高速AD 采样电路

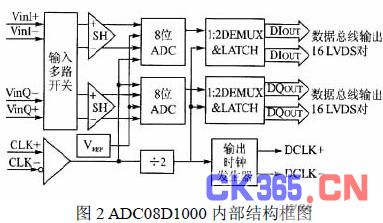

本系统的 AD 采样电路选用的是国家半导体公司于2005 年推出的双通道低功耗的高速8 位A/D 转换器ADC08D1000,其最高单通道采样频率达1.3 GHz,全功率带宽(FPBW)为1.7 GHz,在500 MHz 标准信号输入的情况下可以获得7.4 位的有效采样位数。整个A/D 转换器 用单电源1.9 V 供电,内带高质量参考源和高性能采样保持电路,每个通道均为差分输入,采 样范围可选为650 mV 或870 mV(峰-峰值),而且功耗只有 1.6W。由于这款芯片设有创新的可 全面编程的双边取样功能,只要利用内置的两个转换器进行交替取样,便可将每一通道的取 样速度提高至 2 GSPS。该芯片设有粗略及精细的时间调控功能,让每一通道的取样时钟能以 每一步级为 0.1 微微秒 (pico-second) 的调校幅度各自独立校准。该芯片的三线串行总线控制 取样率的调校幅度、芯片的其他功能以及独立控制的 I 与 Q 通道的增益与补偿微调功能。 由于 ADC08D1000 芯片的功率极低,因此系统设计工程师无需为系统加设散热扇或散热器, 有助节省电路板的板面空间,以及降低产品的开发成本。ADC08D1000 内部结构框图如图2 所示。

1.3FPGA 电路设计

随着可编程器件 FPGA 的集成度和速度不断提高,设计手段也更加完善,FPGA 以其编程 灵活性被广为使用。本设计中FPGA 选用Altera 公司的Stratix 系列的EP1S40 器件,该器件继 承了Altera 公司Stratix 系列的共同优点,由于引入了崭新的自适应逻辑模块(ALM),使得Stratix 有更高的性能和逻辑封装、更少的逻辑和布线级数以及更强的DSP 支持。

本设计中 FPGA 配置方面采用的是主动串行(AS)配置方式与JTAG 方式相结合,可以 通过将FPGA 芯片的MSEL3、MSEL2、MSEL1 和MSEL0 引脚驱动为高电平或低电平来选择 配置的方式,该设计最终选择的是时钟为40MHz 的快速AS 配置。

FPGA 内部功能上,主要根据具体设计方案而定,由于该硬件平台设计考虑到了系统的可 扩展性,从器件的选择上就对系统的资源进行了*估,因此该设计选用的FPGA 从功能设计 上可选性较多,通用性较强,基本上可以实现一般要求下的数字信号的预处理功能。

1.4 DSP 电路设计

该系统 DSP 采用的TI 公司最新推出的高性能定点DSPTMS320C6416,其时钟频率可达 600MHz,最高处理能力为4800MIPS,软件与C62X 完成兼容,采用先进的甚长指令结构(VLIW) 的DSP 内核有6 个ALU(32/40bit),每个时钟周期可以执行8 条指令,所有指令都可以条件 执行[3]。该DSP 具有Viterbi 译码协处理器(VCP)和Turbo 译码协处理器(TCP);采用两级 缓存结构,一级缓存(L1)由128Kbit 的程序缓存和128Kbit 的数据缓存组成,二级缓存(L2) 为8Mbit;有2 个扩展存储器接口(EMIF),一个为64bit(EMIFA),一个为16bit(EMIFA), 可以与异步(SRAM、EPROM)/同步存储器(SDRAM、SBSRAM、ZBTSRAM、FIFO)无缝 连接,最大可寻址范围为1280MB;具有扩展的直接存储器访问控制器(EDMA),可以提供 64 条独立的DMA 通道;主机接口(HPI)总线宽度可由用户配置(32/16bit),具有32bit/33MHz, 3.3V 的PCI 主/从接口,该接口符合PCI 标准2.2 版,有3 个多通道串口(McBSPs),每个 McBSPs 最多可支持256 个通道,能直接与T1/E1、MVIP、SCSA 接口,并且与Motorola 的 SPI 接口兼容,片内还有一个16 针的通用输入输出接口(GPIO)。

1.5 USB 接口电路

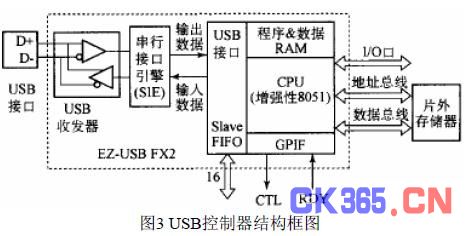

为了可以将采集到的数据可以传给PC机以实时显示,该系统设计了USB接口电路。该接 口电路主要采用了Cypress公司的USB2.0的集成微控制器CY7C68013,它内部集成了1个增强型 的8051、1个智能USB串行接口引擎、1个USB数据收发器、3个8位I/O口、16位地址线、8.5 KB 的RAM和4K的BFIFO等。增强性8051内核完全与标准8051兼容,而性能可达到标准8051的3 倍以上,其框图如图3所示[4]。

2 系统软件设计

2.1 FPGA 内部功能设计

该高速数据采集系统FPGA 内部功能主要包括系统全局时钟模块、PLL 时钟配置模块、 AD 采样配置模块、数据率转换模块以及FIFO 模块。FPGA 程序的开发在QuartusⅡ6.0 环境 下,主要采用了模块化编程与VDHL 语言编程相结合,实现各功能模块开发。

2.2DSP 软件设计

系统采用了 DSP 来完成后续数字信号的处理,根据对高速AD 采集后的数据做相应的数 据预处理,通过中断控制信号来完成对DSP 的启动控制。本设计中的信号处理主要围绕数据 采集预处理后的I、Q 信号量进行一系列的处理,包括每一路信号的瞬时幅度、瞬时相位、瞬 时频率以及对采样信号的频谱的分析(FFT 变换)等的处理。

2.3 USB 程序设计

该系统的软件设计主要包括两部分,一部分是固件设计,另一部分是驱动和应用程序。 本方案中的固件设计思路是:在Cypress公司自己提供的固件开发软件平台上,结合该固件工 程所提供的FW.C,BUI K.C,DSCR.A51,FX2.H,FX2REGS.H等文件,运用高级语言C51进 行编程。固件程序的载入方式为:使用CY7C68013特有的软配置功能,将固件程序存储到计 算机中,当设备接入USB电缆时,通过Cypress公司提供的开发软件Usb Control Panel的 Download项,将固件载入到控制芯片中[5]。

系统的驱动程序部分用Windows2000 DDK编写,控制USB接口的工作。在驱动程序的设 计中使用了EZ-loader,它能在Windows驱动程序装入以后,第一次先加载EZ-loader,进行第一 次“枚举”,然后由EZ-loader再加载本来的固件程序,让系统进行第二次“枚举”。

高级应用程序建立在驱动程序之上,选用VC++6.0的开发环境来开发应用程序。它以驱动 程序为桥梁,对USB设备进行命令控制,处理USB设备传回的数据,例如波形显示,频谱分析 等。

3 实验测试结果

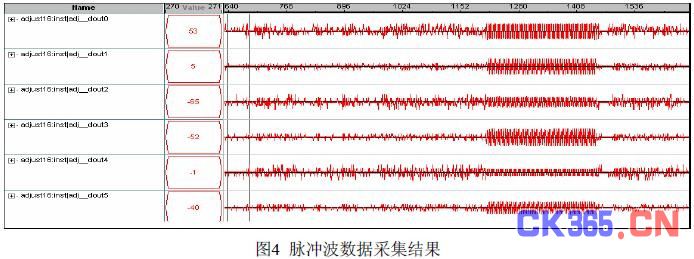

在完成了超高速数据采集与处理系统的设计与调试的基础上,对该系统的数据采集情况 进行了实际测试。输入信号形式:脉冲波;载波频率:100MHz;重复周期:1ms;脉宽:100us。 将预先编好的程序下载到FPGA中,并通过SignalTapⅡ嵌入式逻辑分析观察数据采集的波形。 其中触发信号频率为125MHz,观察信号为AD采样数据经过数据率转换模块后的多路信号波 形,图4为数据采集结果。

4 结论

介绍了一种基于FPGA的超高速数据采集与处理系统,对系统各部分电路设计进行了详细 阐述,并对后续处理系统的功能做了简要介绍。在Quartus6.0环境下采用了模块化编程与VDHL 语言编程相结合实现系统功能开发,并借助SignalTapⅡ嵌入式逻辑分析仪对高速采样系统进 行了测试,测试结果正确。该超高速数据采集与处理系统可以通过修改FPGA内部程序来实现 其它功能扩展,并利用后续DSP的强大实时处理能力,完成更为复杂的数字信号处理。因此该 系统在工程应用上具有较强的通用性。